# MSM6100<sup>™</sup> Mobile Station Modem

## **Device Specification (Advance Information)**

80-V4689-1 Rev. D

March 14, 2003

**QUALCOMM** Proprietary

**Restricted Distribution.** This document contains critical information about QUALCOMM products and may not be distributed to anyone that is not an employee of QUALCOMM without the approval of Configuration Management.

QUALCOMM Incorporated 5775 Morehouse Drive San Diego, CA 92121-1714 U.S.A. QUALCOMM Incorporated 5775 Morehouse Drive San Diego, CA 92121-1714 U.S.A.

Copyright © 2003 QUALCOMM Incorporated. All rights reserved.

All data and information contained in or disclosed by this document are confidential and proprietary information of QUALCOMM Incorporated, and all rights therein are expressly reserved. By accepting this material, the recipient agrees that this material and the information contained therein are held in confidence and in trust and will not be used, copied, reproduced in whole or in part, nor its contents revealed in any manner to others without the express written permission of QUALCOMM Incorporated.

Export of this technology may be controlled by the United States Government. Diversion contrary to U.S. law prohibited.

**Restricted Distribution.** This document contains critical information about QUALCOMM products and may not be distributed to anyone that is not an employee of QUALCOMM without the approval of Configuration Management.

QUALCOMM is a registered trademark and registered service mark of QUALCOMM Incorporated. Other product and brand names may be trademarks or registered trademarks of their respective owners.

Information in this document is preliminary and subject to change and does not represent a commitment on the part of QUALCOMM Incorporated.

#### Submit Technical Questions at: https://support.cdmatech.com

MSM6100<sup>TM</sup> Device Specification (Advance Information)

80-V4689-1 Rev. D

# Contents

### Preface

| About this Technical Manualxiii |

|---------------------------------|

|---------------------------------|

#### 1 Overview

| 1.1 | Applicati | on Description                                      | 1-1 |

|-----|-----------|-----------------------------------------------------|-----|

| 1.2 | MSM610    | 0 Features                                          | 1-3 |

|     | 1.2.1     | MSM6100 General Features                            | 1-3 |

|     | 1.2.2     | IS-2000 1X Features Supported by the MSM6100 Device | 1-4 |

|     | 1.2.3     | MSM6100 Audio Processing Features                   | 1-4 |

|     | 1.2.4     | MSM6100 Microprocessor Subsystem                    | 1-5 |

|     | 1.2.5     | Supported Interface Features                        | 1-5 |

|     | 1.2.6     | Supported Multimedia Features                       | 1-6 |

|     | 1.2.7     | gpsOne <sup>TM</sup> Technology                     | 1-6 |

|     | 1.2.8     | radioOne <sup>TM</sup> Technology                   | 1-7 |

## 2 Pin Descriptions

| 2.1 | I/O Description Parameters                        | 2-1  |  |

|-----|---------------------------------------------------|------|--|

|     | Pin Names and Pinouts                             |      |  |

| 2.3 | 341-Ball CSP Pinout for MSM6100 Device (Top View) | 2-11 |  |

## **3 Electrical Specifications**

| 3.1 | DC Elect | trical Specifications            |  |

|-----|----------|----------------------------------|--|

|     | 3.1.1    | Absolute Maximum Ratings         |  |

|     | 3.1.2    | Recommended Operating Conditions |  |

|     | 3.1.3    | DC Characteristics               |  |

|     | 3.1.4    | GPADC Specifications             |  |

|     | 3.1.5    | CODEC Specifications             |  |

|     | 3.1.6    | Power Consumption                |  |

| 3.2 | Timing C | Characteristics                  |  |

|     | 3.2.1    | Measurement Conditions           |  |

|     |          |                                  |  |

|   |     | 3.2.2      | Bus Rise and Fall Times                               | 3-29  |

|---|-----|------------|-------------------------------------------------------|-------|

|   |     | 3.2.3      | Clock Jitter                                          | 3-29  |

|   |     | 3.2.4      | TCXO Timing                                           | 3-30  |

|   |     | 3.2.5      | MCLK Timing                                           |       |

|   |     | 3.2.6      | PCM Interface                                         | 3-31  |

|   |     | 3.2.7      | Auxiliary PCM Interface                               | 3-33  |

|   |     | 3.2.8      | External Bus Interface 1 (EBI1)                       | 3-35  |

|   |     | 3.2.9      | External Bus Interface 2 (EBI2)                       | 3-51  |

|   |     | 3.2.10     | JTAG Timing                                           | 3-123 |

| 4 | MSN | 16100 Inte | rface Descriptions                                    |       |

|   | 4.1 | Overview   |                                                       | 4-2   |

|   | 4.2 | MSM610     | 0 Mobile Station Modem ASIC Overview                  | 4-3   |

|   | 4.3 | RF Interfa | ace                                                   | 4-5   |

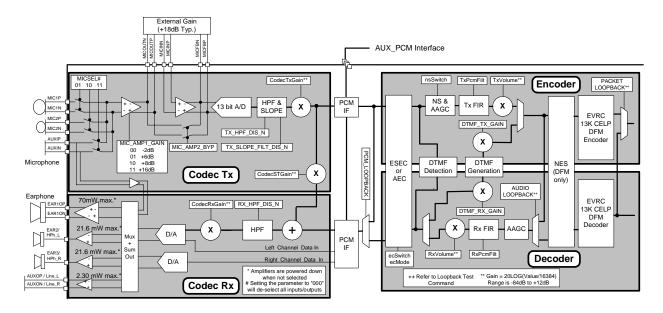

|   | 4.4 | Stereo Wi  | deband CODEC                                          | 4-9   |

|   |     | 4.4.1      | Transmit Path Processing                              | 4-10  |

|   |     | 4.4.2      | Receive Path Processing                               | 4-14  |

|   |     | 4.4.3      | Microphone and Earphone Interface                     | 4-15  |

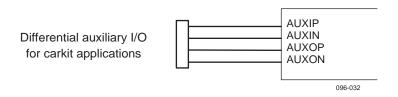

|   |     | 4.4.4      | Auxiliary I/O Interface                               | 4-16  |

|   |     | 4.4.5      | Digital PCM Interface                                 | 4-16  |

|   |     | 4.4.6      | Primary PCM Operation                                 | 4-17  |

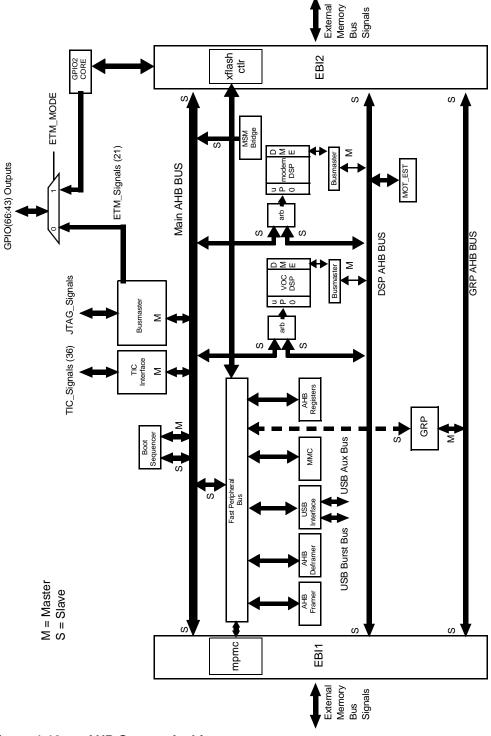

|   | 4.5 | ARM Mic    | croprocessor and Peripherals and AHB                  | 4-18  |

|   |     | 4.5.1      | AHB System                                            | 4-18  |

|   |     | 4.5.2      | ARM926EJ-S                                            | 4-21  |

|   |     | 4.5.3      | MAIN AHB Bus Masters                                  | 4-22  |

|   |     | 4.5.4      | DSP AHB Bus Masters                                   | 4-22  |

|   |     | 4.5.5      | GRP AHB Bus Masters                                   | 4-22  |

|   |     | 4.5.6      | Memory Map and Memory Map Decoder                     | 4-22  |

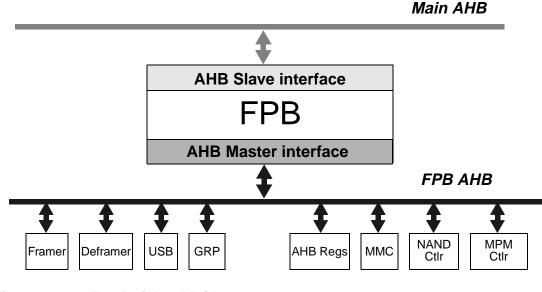

|   |     | 4.5.7      | Fast Peripheral Bridge                                | 4-26  |

|   |     | 4.5.8      | ARM Clock and Power Management                        | 4-27  |

|   |     | 4.5.9      | Reset and Pause                                       | 4-28  |

|   |     | 4.5.10     | Watchdog Timer                                        | 4-29  |

|   |     | 4.5.11     | MSM6100 Reset Scheme Summary                          | 4-31  |

|   |     | 4.5.12     | Interrupt Controller                                  | 4-32  |

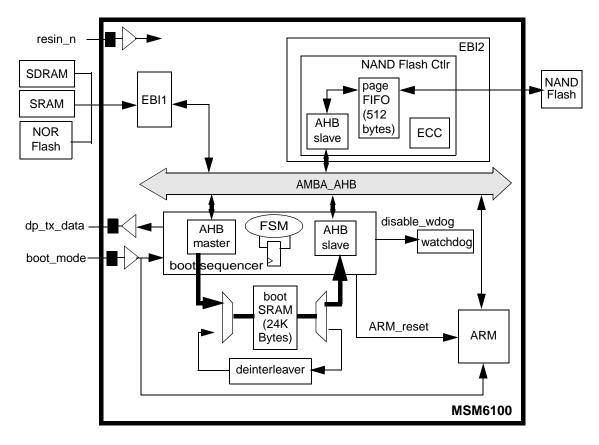

|   | 4.6 | Boot Met   | hodology                                              | 4-39  |

|   |     | 4.6.1      | Overview                                              |       |

|   |     | 4.6.2      | Pin Requirements                                      | 4-39  |

|   |     | 4.6.3      | Hardware Support                                      | 4-41  |

|   |     | 4.6.4      | The Sequence of Events of Booting From the NOR Flash  | 4-41  |

|   |     | 4.6.5      | The Sequence of Events of Booting From the NAND Flash | 4-42  |

|      | 4.6.6      | Other Requirements                                 | 4-43  |

|------|------------|----------------------------------------------------|-------|

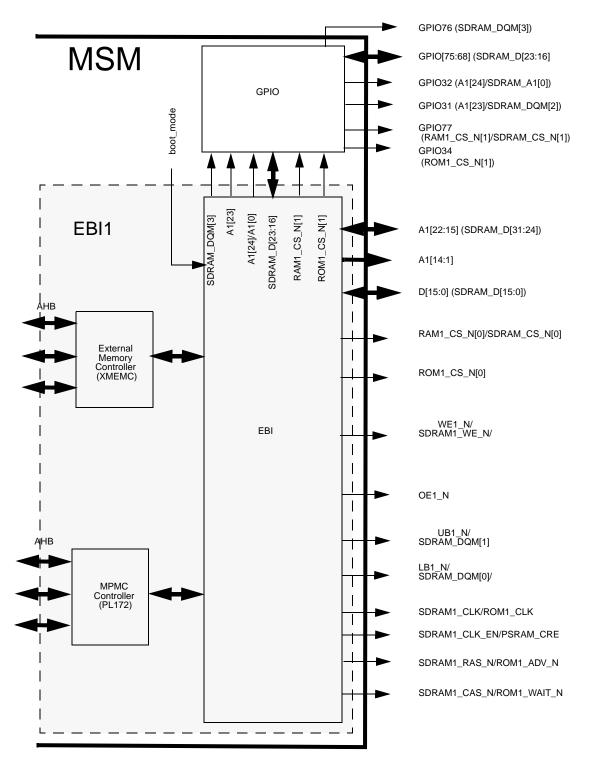

| 4.7  | External E | Bus Interface 1                                    |       |

|      | 4.7.1      | Features                                           | 4-44  |

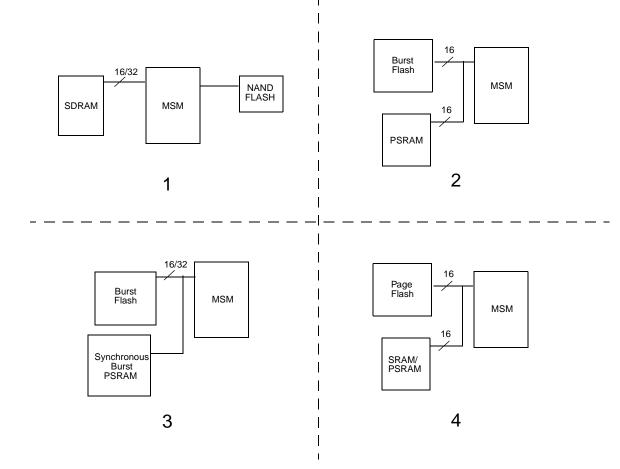

|      | 4.7.2      | Memories Supported on EBI1                         | 4-44  |

|      | 4.7.3      | EBI1 System                                        |       |

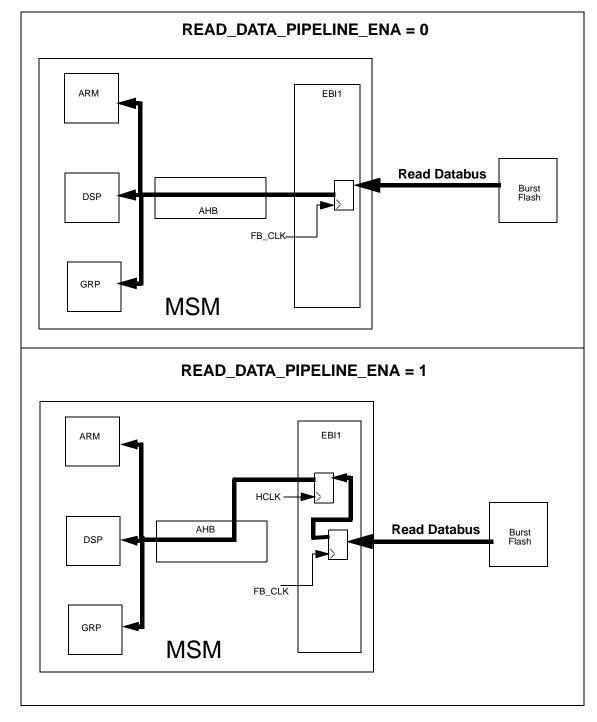

|      | 4.7.4      | External Memory Controller (XMEMC)                 | 4-50  |

|      | 4.7.5      | ARM's Multi-Port Memory Controller (MPMC) or PL172 |       |

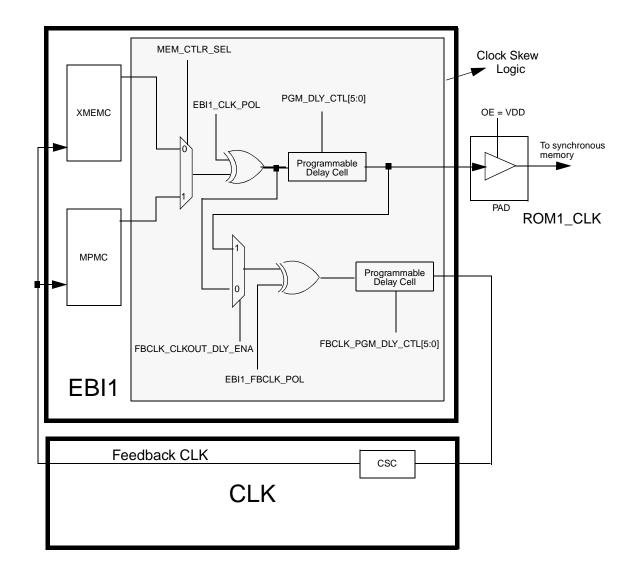

|      | 4.7.6      | EBI1 Clock Skew Block                              |       |

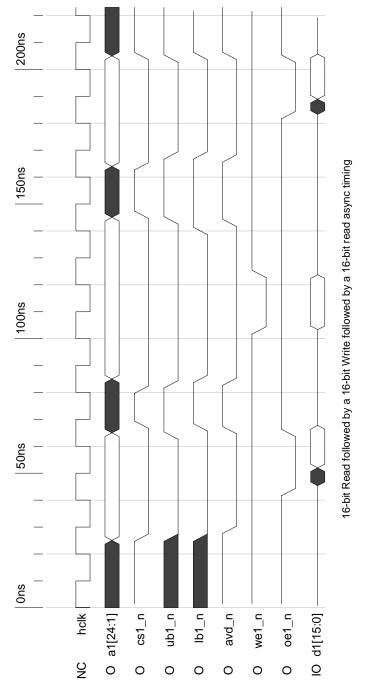

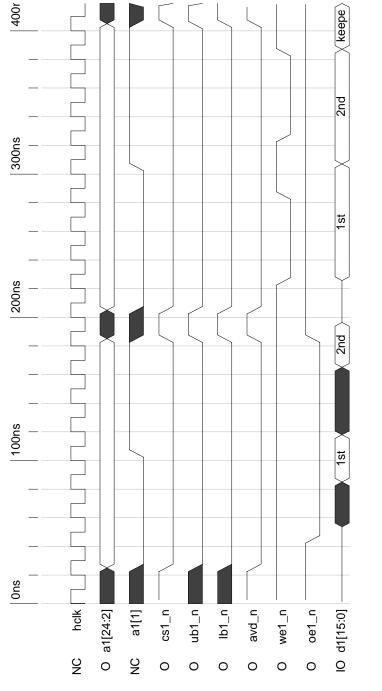

|      | 4.7.7      | Interface Timing Diagrams                          | 4-70  |

| 4.8  | External E | Bus Interface 2                                    |       |

|      | 4.8.1      | Features                                           |       |

|      | 4.8.2      | Chip Selects                                       |       |

|      | 4.8.3      | Access Types                                       |       |

|      | 4.8.4      | EBI2 System                                        |       |

|      | 4.8.5      | EBI2 External Memory Controller                    |       |

|      | 4.8.6      | NAND Flash Memory Interface                        |       |

| 4.9  | Mode Sele  | ect and Emulation Considerations                   | 4-99  |

|      | 4.9.1      | Mode Selection Inputs                              | 4-99  |

|      | 4.9.2      | NATIVE Mode                                        | 4-100 |

|      | 4.9.3      | MSM6100 ETM Mode                                   | 4-100 |

|      | 4.9.4      | JTAG Emulation                                     | 4-103 |

| 4.10 | UART, R-   | UIM, and USB Interfaces                            |       |

|      | 4.10.1     | UART1                                              |       |

|      | 4.10.2     | UART2 and UART3                                    |       |

|      | 4.10.3     | R-UIM                                              |       |

|      | 4.10.4     | USB Interface                                      |       |

| 4.11 | User Inter | face                                               |       |

|      | 4.11.1     | Keypad Interface                                   |       |

|      | 4.11.2     | Ringer                                             |       |

|      | 4.11.3     | M/N Counter                                        |       |

|      | 4.11.4     | I2C                                                | 4-124 |

|      | 4.11.5     | I2S                                                | 4-124 |

|      | 4.11.6     | MultiMediaCard Controller                          |       |

| 4.12 | HKADC.     |                                                    |       |

|      | 4.12.1     | Analog Input Voltage Range                         |       |

|      | 4.12.2     | HKADC Operation                                    | 4-130 |

|      | 4.12.3     | HKADC Conversion Time                              | 4-131 |

|      | 4.12.4     | HKADC Analog Interface Considerations              |       |

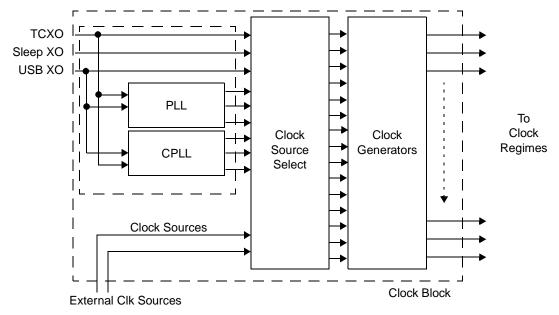

| 4.13 | Clock Reg  | gime                                               | 4-133 |

|      | 4.13.1     | ТСХО                                               | 4-133 |

|      | 4.13.2    | CODEC PLL                            |       |

|------|-----------|--------------------------------------|-------|

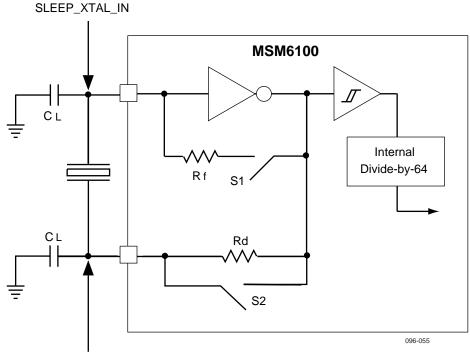

|      | 4.13.3    | SLEEP Crystal Circuit for 32.768 kHz | 4-134 |

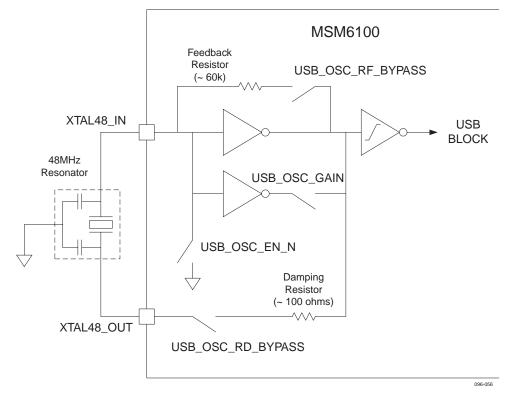

|      | 4.13.4    | USB Crystal Circuit for 48 MHz       | 4-136 |

|      | 4.13.5    | Clock                                |       |

|      | 4.13.6    | Subsystem Clock Regimes              | 4-140 |

| 4.14 | JTAG Inte | erface                               | 4-148 |

|      | 4.14.1    | Test Access Port                     |       |

|      | 4.14.2    | TAP Controller                       |       |

|      | 4.14.3    | Data Registers                       | 4-152 |

|      | 4.14.4    | JTAG Instructions                    |       |

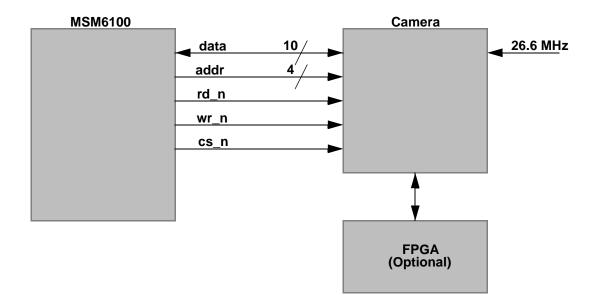

| 4.15 | Camera Ir | nterface                             |       |

|      | 4.15.1    | CAMIF Control                        |       |

|      | 4.15.2    | Output Buffer                        |       |

|      | 4.15.3    | Supported Interface Detail           |       |

|      |           |                                      |       |

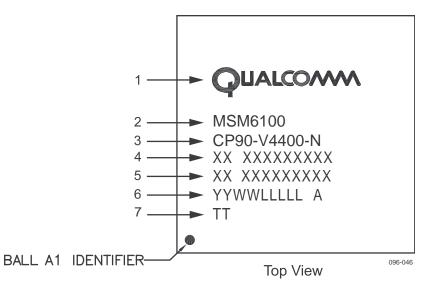

### **5** Mechanical Dimensions

| 5.1 | 341-Ball CSP Package Outline | 5-1 |

|-----|------------------------------|-----|

| 5.2 | 341-Ball CSP Land Pattern    | 5-1 |

| 5.3 | Part Marking                 | 5-2 |

## Figures

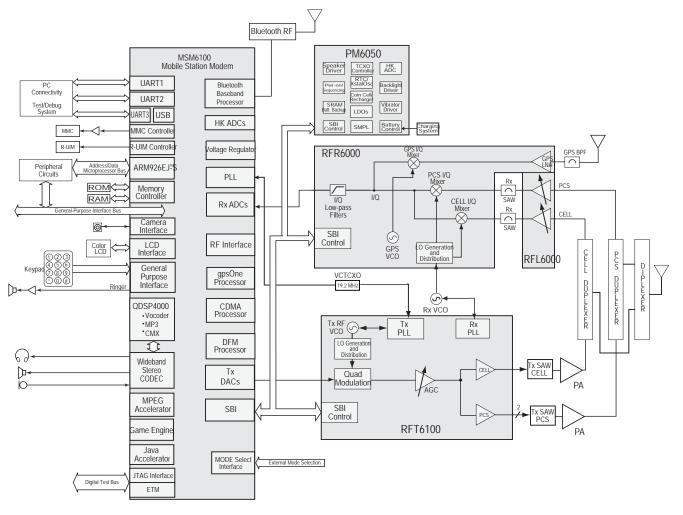

| Figure 1-1  | MSM6100 Device Functional Block Diagram                                                    | 1-3  |

|-------------|--------------------------------------------------------------------------------------------|------|

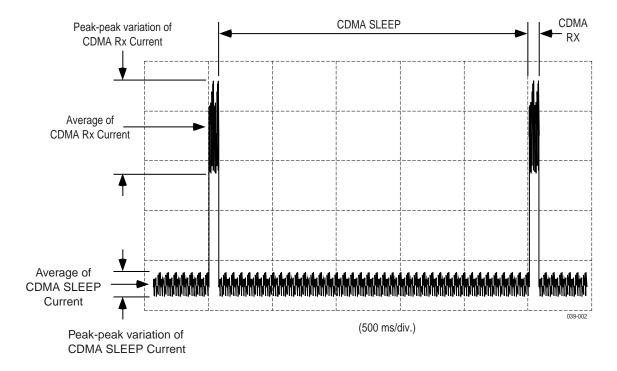

| Figure 3-1  | Power Supply Current versus Time in Slotted Paging Mode                                    | 3-28 |

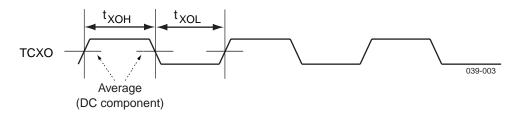

| Figure 3-2  | TCXO Timing Parameters                                                                     | 3-30 |

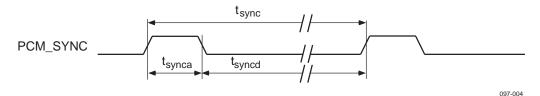

| Figure 3-3  | PCM_SYNC Timing                                                                            | 3-31 |

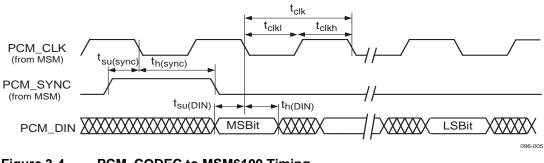

| Figure 3-4  | PCM_CODEC to MSM6100 Timing                                                                | 3-31 |

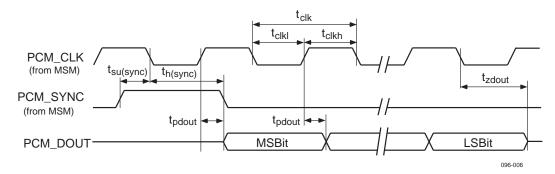

| Figure 3-5  | MSM6100 to PCM_CODEC Timing                                                                | 3-32 |

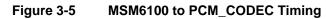

| Figure 3-6  | AUX_PCM_SYNC Timing                                                                        | 3-33 |

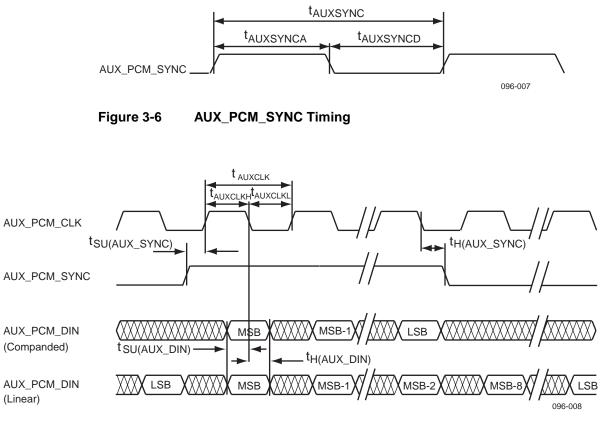

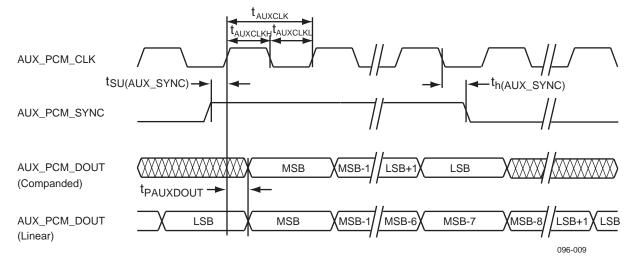

| Figure 3-7  | CODEC to MSM6100 Timing via AUX_CODEC (MSM6100 Receiving)                                  | 3-33 |

| Figure 3-8  | MSM6100 to CODEC Timing via AUX_CODEC (MSM6100 Transmitting).                              | 3-34 |

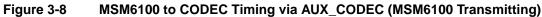

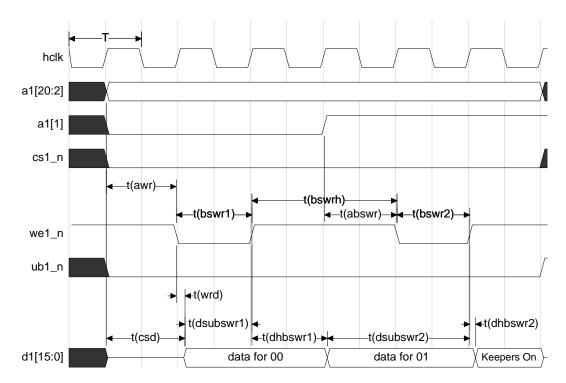

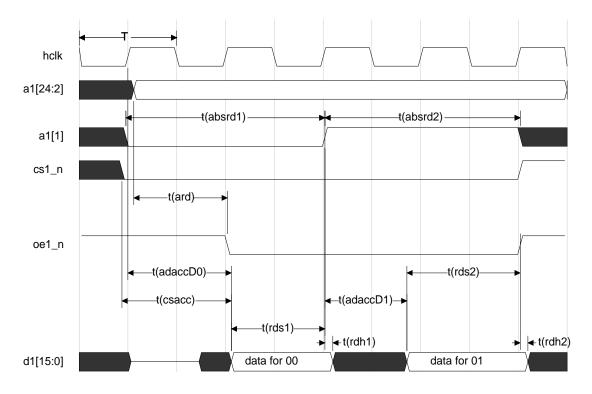

| Figure 3-9  | 16-bit Read Followed by 16-Bit Write Access (Async)                                        | 3-36 |

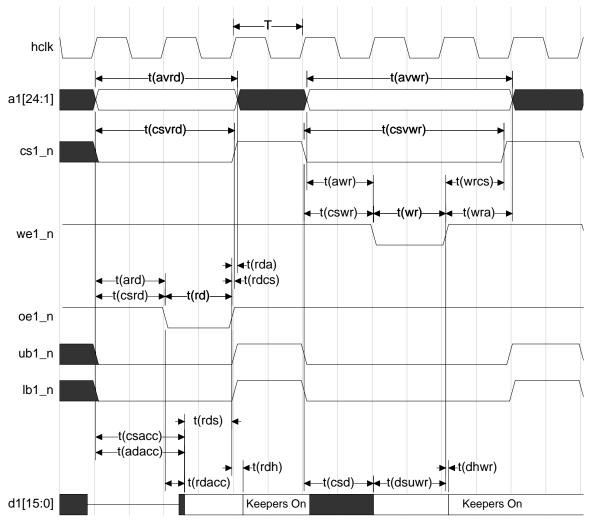

| Figure 3-10 | 16-bit Write Followed by 16-Bit Read Access (Async)                                        | 3-37 |

| Figure 3-11 | Word Bus Sized Write Access to 16-Bit Memory (Async)                                       | 3-41 |

| Figure 3-12 | Word (32-Bit) Read Access From 16 Bit Memory (Async)                                       | 3-42 |

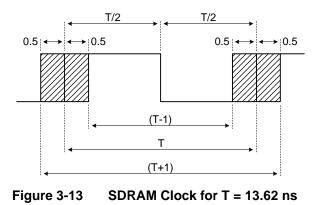

| Figure 3-13 | SDRAM Clock for T = 13.62 ns                                                               | 3-44 |

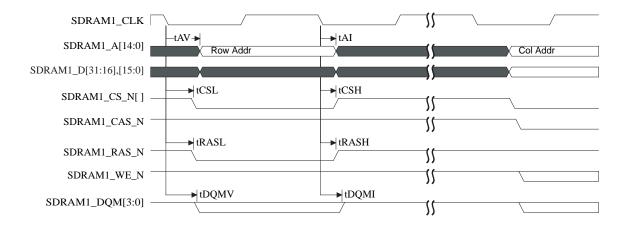

| Figure 3-14 | SDRAM RAS Timing                                                                           | 3-45 |

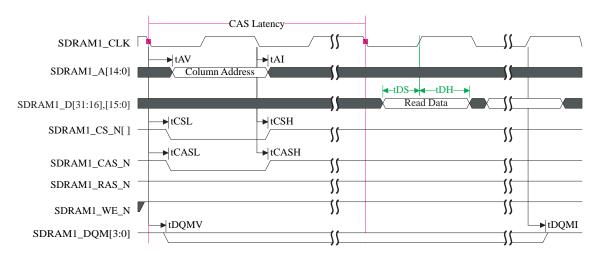

| Figure 3-15 | SDRAM Read Access Timing                                                                   | 3-45 |

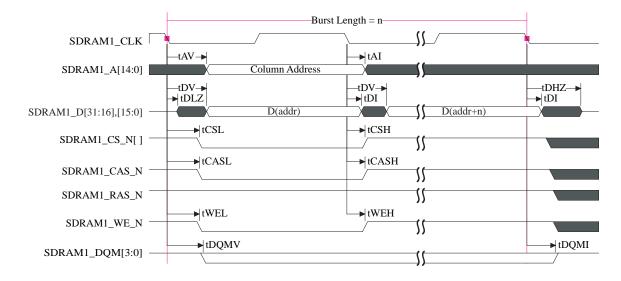

| Figure 3-16 | SDRAM Write Access Timing                                                                  | 3-46 |

| Figure 3-17 | Burst Memory Read Timing                                                                   | 3-47 |

| Figure 3-18 | Burst Memory Write Timing                                                                  | 3-48 |

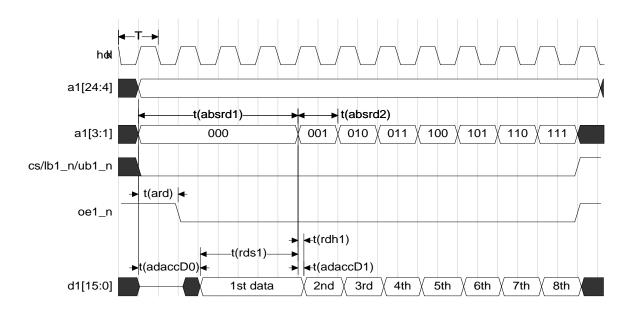

| Figure 3-19 | Page (Page Size = 8 HWORDS) Mode Read Timing<br>for a 4-Word (32-bit) Burst                | 3-50 |

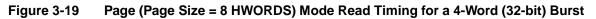

| Figure 3-20 | Page (Page Size = 8 HWORDS) Mode Read Timing<br>for an 8-Word (32-Bit) Burst               |      |

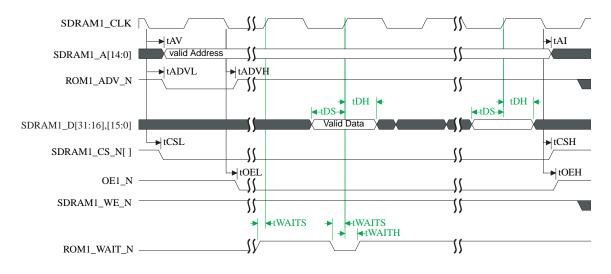

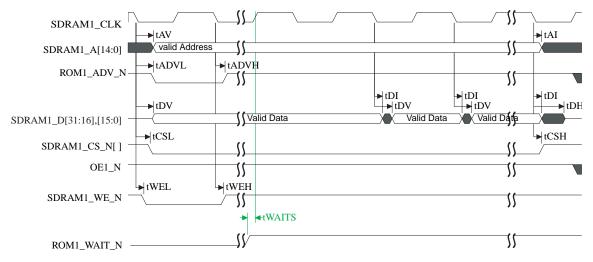

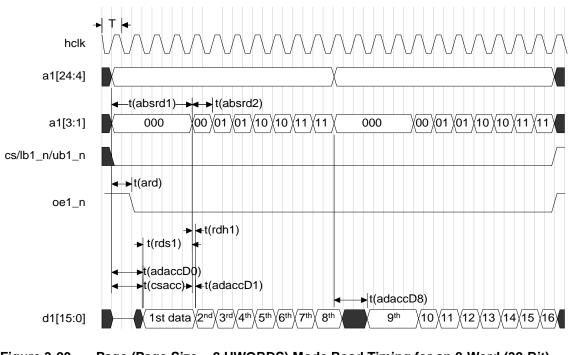

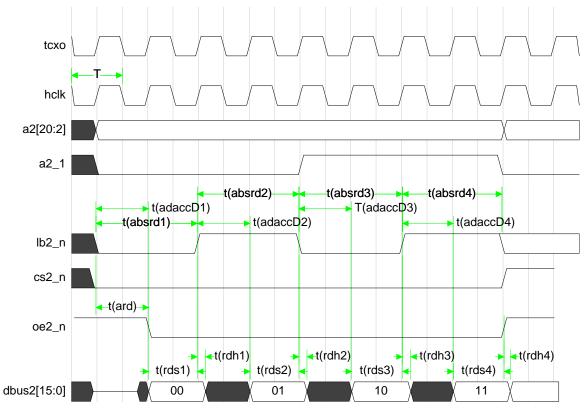

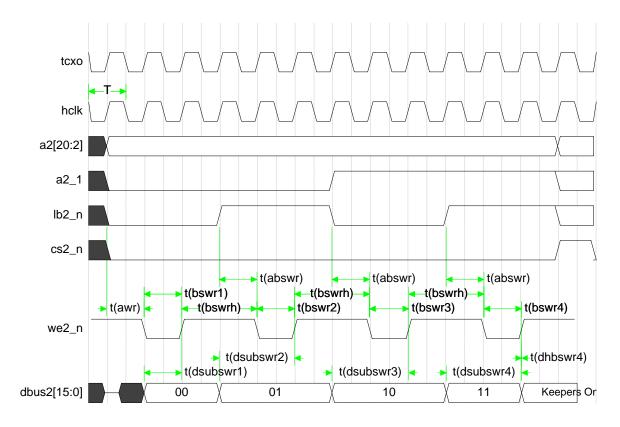

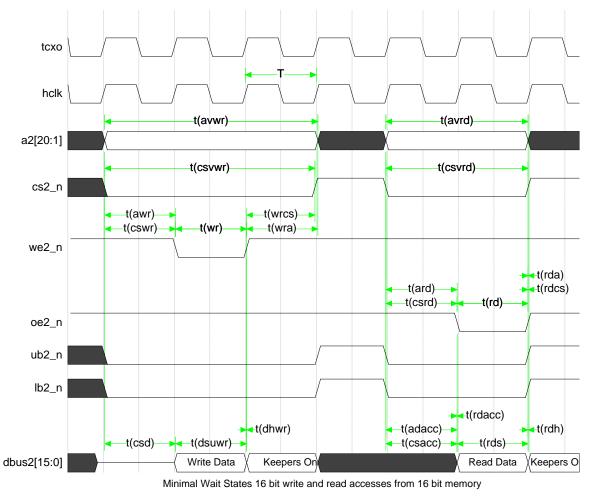

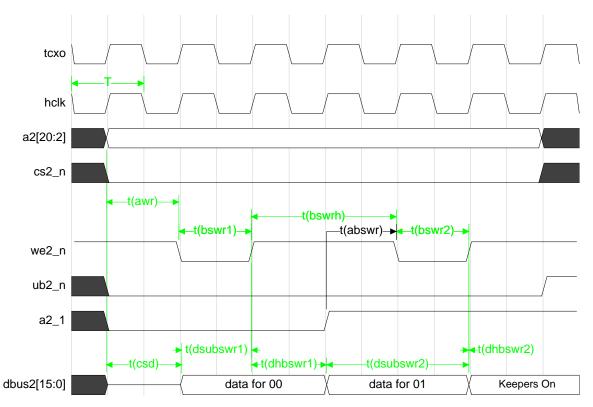

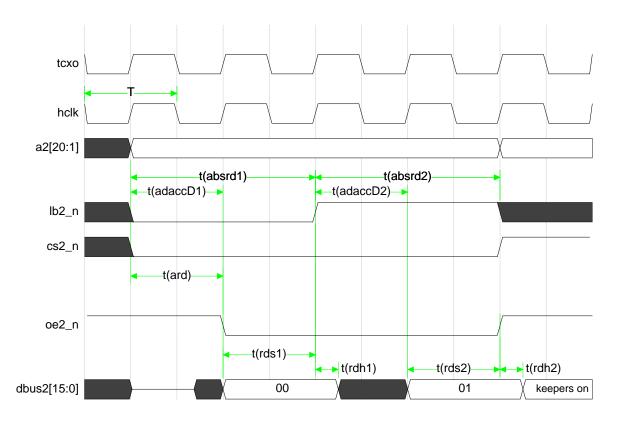

| Figure 3-21 | EBI2 Minimal Wait States 16-bit Write and Read Accesses                                    |      |

| riguie 5-21 | From 16-Bit Memory                                                                         | 3-55 |

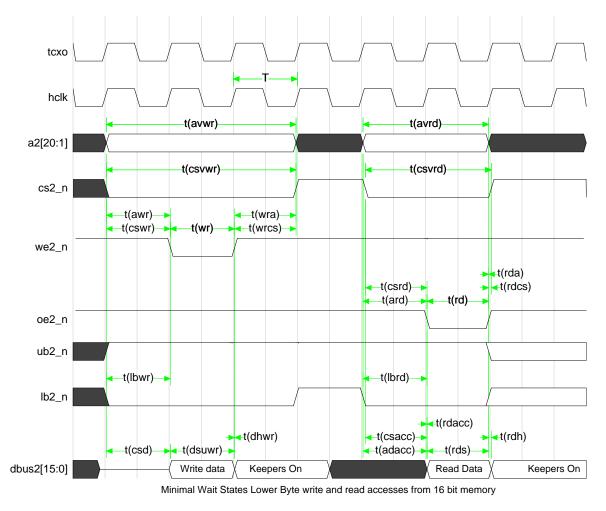

| Figure 3-22 | EBI2 Minimal Wait States Lower Byte Write and Read Accesses                                |      |

| 0           | From 16-Bit Memory                                                                         | 3-56 |

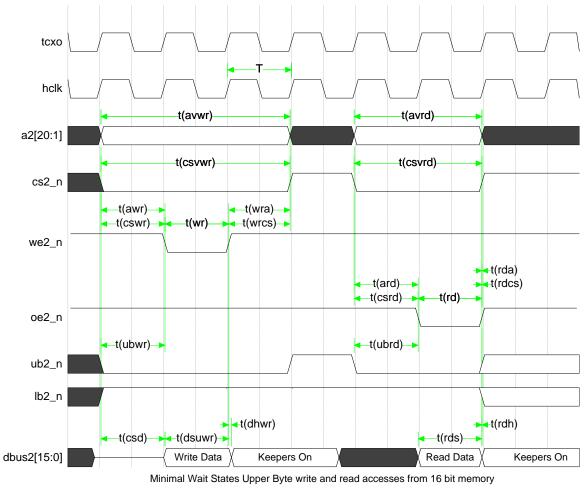

| Figure 3-23 | EBI2 Minimal Wait States Upper Byte Write and Read Accesses                                |      |

|             | From 16-Bit Memory                                                                         | 3-57 |

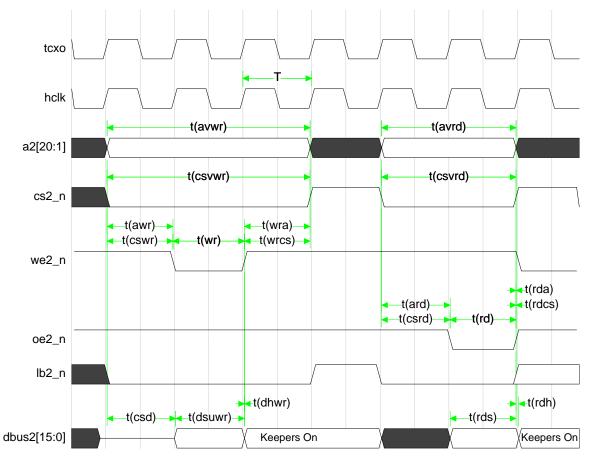

| Figure 3-24 | EBI2 Minimal Wait States 8-bit Write and Read Accesses (Even Address)<br>From 8-Bit Memory | 3-58 |

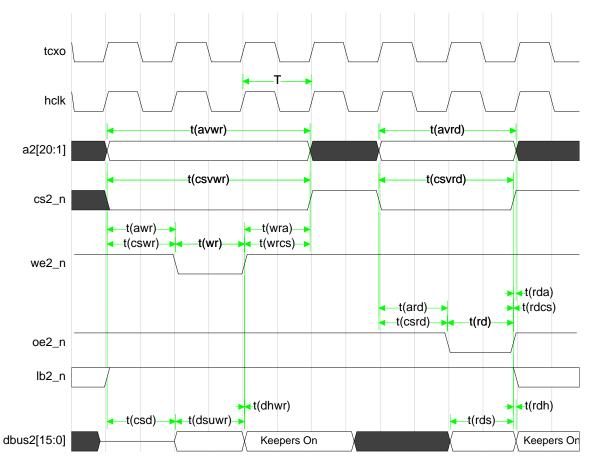

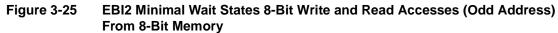

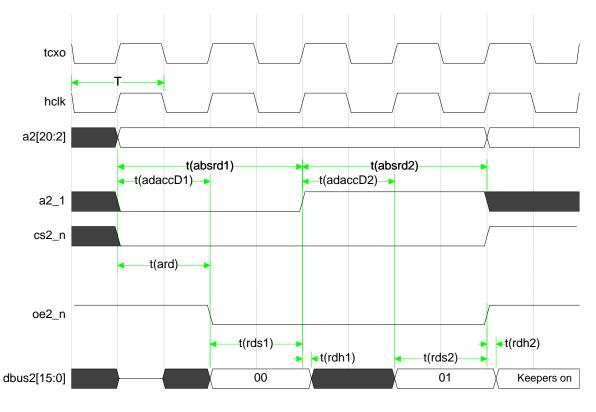

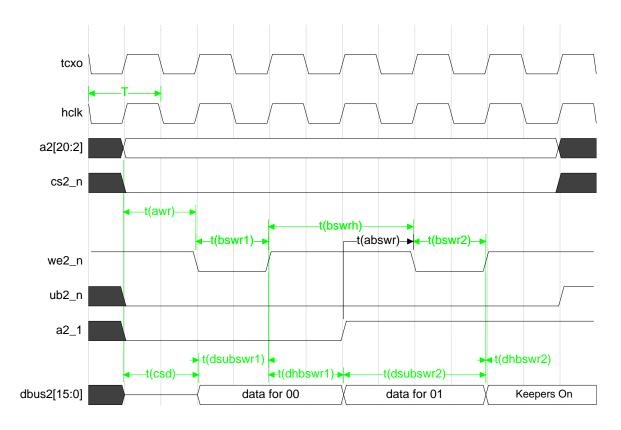

| Figure 3-25 | EBI2 Minimal Wait States 8-Bit Write and Read Accesses (Odd Address)                       |      |

| U           | From 8-Bit Memory                                                                          | 3-59 |

| Figure 3-26 | EBI2 Word Read Access From 16-Bit Memory                                                   | 3-61 |

| Figure 3-27 | EBI2 Word Bus Sized Write Access to 16-Bit Memory                                          | 3-62 |

| Figure 3-28 | EBI2 Half Word Read Access From 8-Bit Memory                                               | 3-63 |

| Figure 3-29 | EBI2 Half Word Bus Sized Write Access to 8-Bit Memory                                      | 3-64 |

| Figure 3-30 | EBI2 Word Read Access From 8-Bit Memory                                                    |      |

| Figure 3-31 | EBI2 Word Write Access to 8-Bit Memory                                                     | 3-66 |

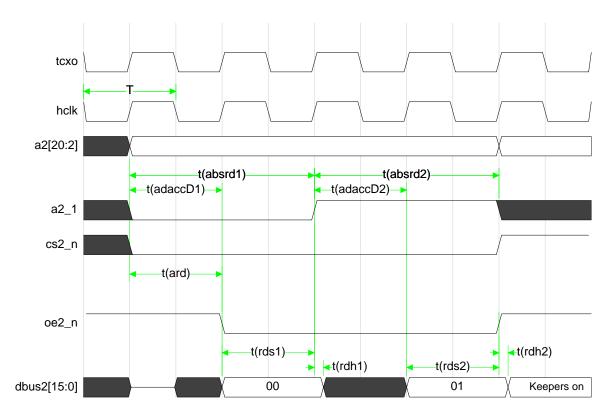

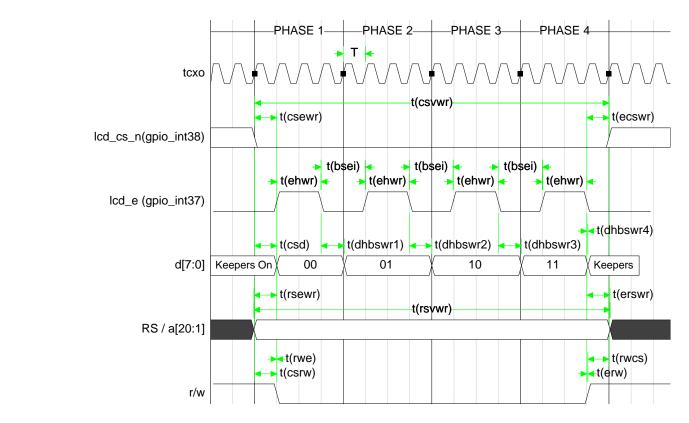

| Figure 3-32 | Intel LCD Interface NATIVE Write and Read Timing                                                                           | 3-73  |

|-------------|----------------------------------------------------------------------------------------------------------------------------|-------|

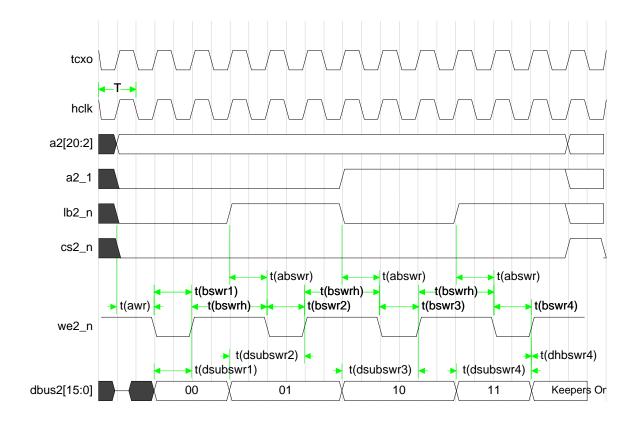

| Figure 3-33 | Intel LCD Interface Bus Sized 32x16 Write Timing                                                                           | 3-75  |

| Figure 3-34 | Intel LCD Interface Bus Sized 32x16 Read Timing                                                                            | 3-76  |

| Figure 3-35 | Intel LCD Interface Bus Sized 32x8 Write Timing                                                                            | 3-77  |

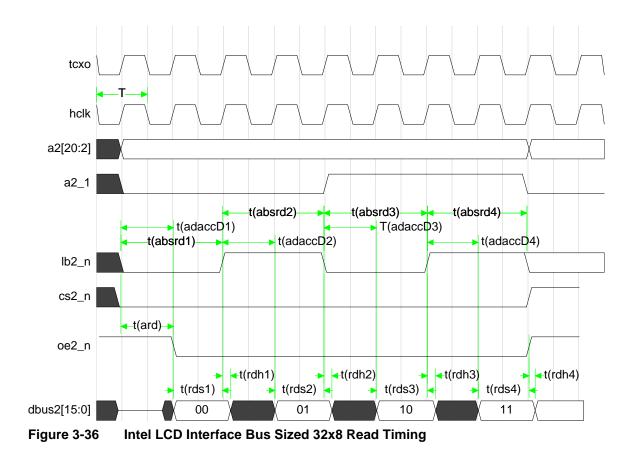

| Figure 3-36 | Intel LCD Interface Bus Sized 32x8 Read Timing                                                                             | 3-78  |

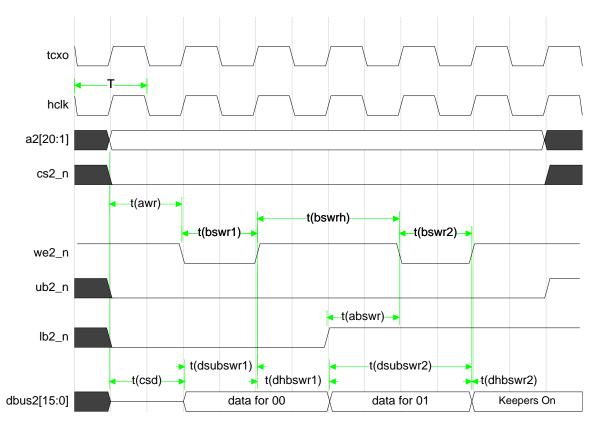

| Figure 3-37 | Intel LCD Interface Bus Sized 16x8 Write Timing                                                                            | 3-79  |

| Figure 3-38 | Intel LCD Interface Bus Sized 16x8 Read Timing                                                                             | 3-80  |

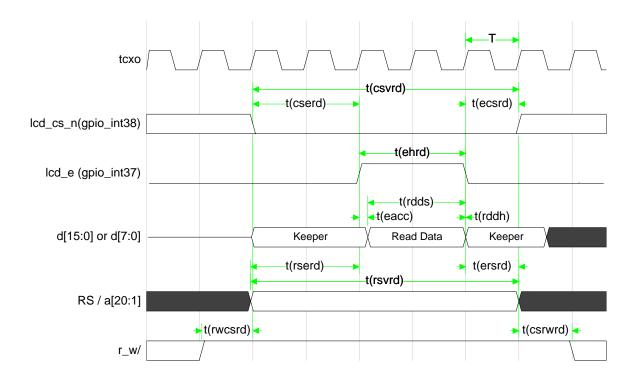

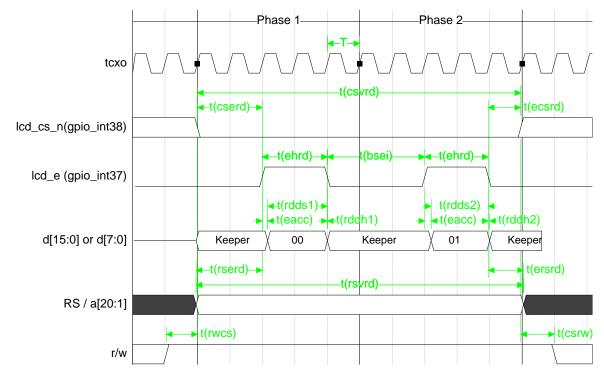

| Figure 3-39 | Motorola LCD Interface NATIVE Read Timing                                                                                  | 3-84  |

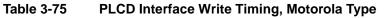

| Figure 3-40 | Motorola LCD Interface NATIVE Write Timing                                                                                 | 3-85  |

| Figure 3-41 | Motorola LCD Interface Bus Sized 32x16 or 16x8 Read Timing                                                                 | 3-87  |

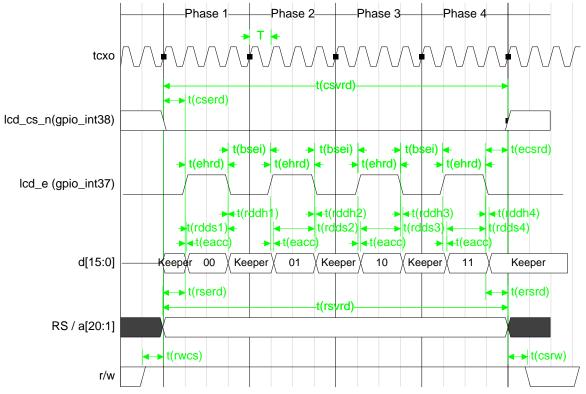

| Figure 3-42 | Motorola LCD Interface Bus Sized 32x8 Read Timing                                                                          | 3-88  |

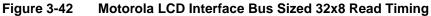

| Figure 3-43 | Motorola LCD Interface Bus Sized 32x16 or 16x8 Write Timing                                                                | 3-90  |

| Figure 3-44 | Motorola LCD Interface Bus Sized 32x8 Write Timing                                                                         | 3-91  |

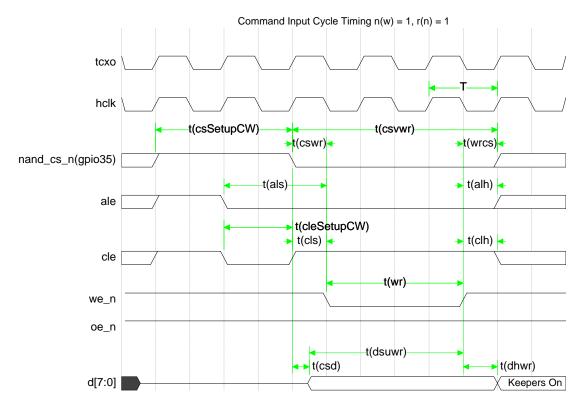

| Figure 3-45 | NAND Command Write Timing with 3 Access Cycles                                                                             |       |

|             | (Minimum Access Cycles + 1 Access WS) and 1 Recovery Cycle                                                                 | 3-96  |

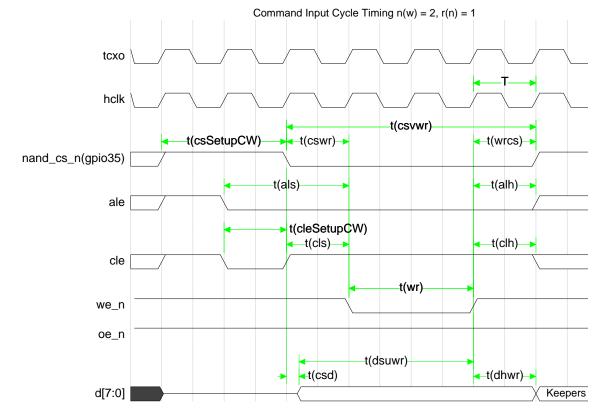

| Figure 3-46 | NAND Command Write Timing with 4 Access Cycles                                                                             |       |

|             | (Minimum Access Cycles + 2 Access WS) and 1 Recovery Cycle                                                                 | 3-98  |

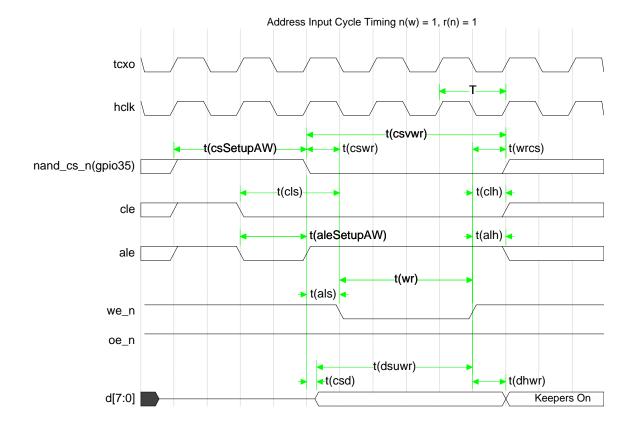

| Figure 3-47 | NAND Address Write Timing with 3 Access Cycles                                                                             |       |

|             | (Minimum Access Cycles + 1 Access WS) and 1 Recovery Cycle                                                                 | 3-100 |

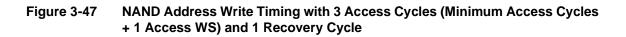

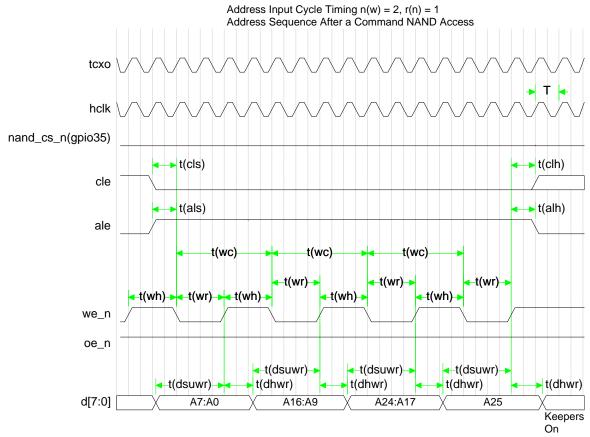

| Figure 3-48 | NAND Address Write Timing with 4 Access Cycles                                                                             | 2 102 |

| E' 2.40     | (Minimum Access Cycles + 2 Access WS) and 1 Recovery Cycle                                                                 | 3-102 |

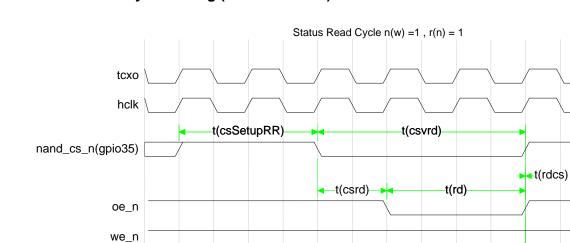

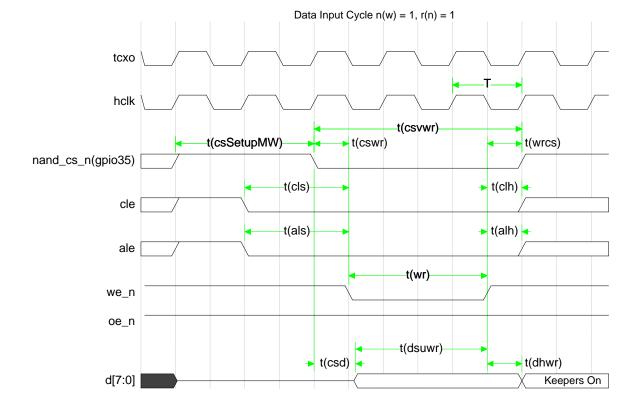

| Figure 3-49 | NAND Command Data Read Timing with 3 Access Cycles<br>(Minimum Access Cycles + 1 Access WS) and 1 Recovery Cycle           | 3 104 |

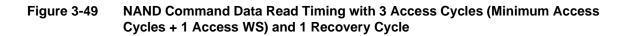

| Figure 3-50 | NAND ID Data Read Timing with 3 Access Cycles                                                                              |       |

| Figure 5-50 | (Minimum Access Cycles + 1 Access WS) and 1 Recovery Cycle                                                                 | 3-105 |

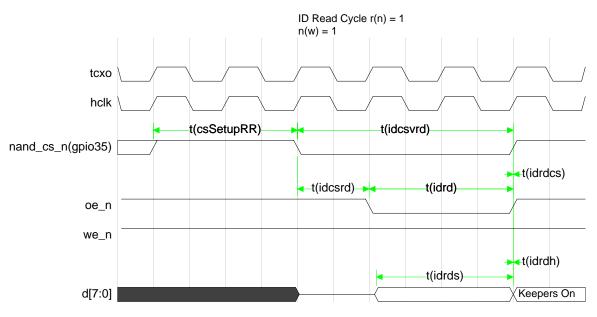

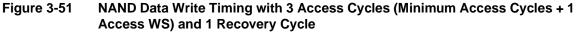

| Figure 3-51 | NAND Data Write Timing with 3 Access Cycles                                                                                |       |

| 118010 5 51 | (Minimum Access Cycles + 1 Access WS) and 1 Recovery Cycle                                                                 | 3-106 |

| Figure 3-52 | NAND Data Write Timing with 4 Access Cycles                                                                                |       |

| U           | (Minimum Access Cycles + 2 Access WS) and 1 Recovery Cycle                                                                 | 3-107 |

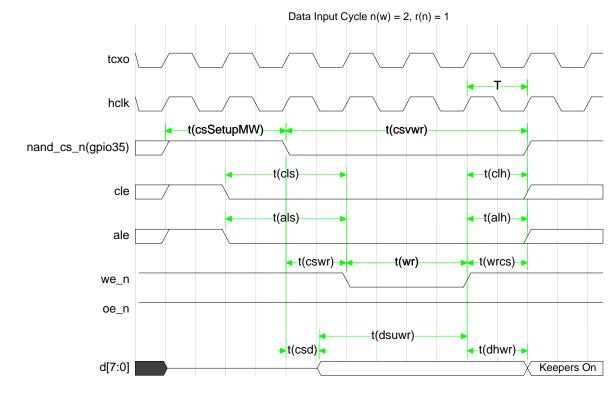

| Figure 3-53 | NAND Memory Data Read Timing (All Accesses)                                                                                | 3-109 |

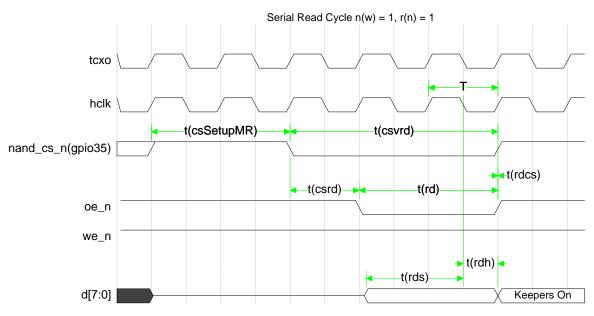

| Figure 3-54 | Consecutive NAND Address Write Timing with 3 Access Cycles                                                                 |       |

|             | (Minimum Access Cycles + 1 Access WS)                                                                                      | 3-110 |

| Figure 3-55 | Consecutive NAND Address Write Timing with 4 Access Cycles                                                                 |       |

|             | (Minimum Access Cycles + 2 Access WS)                                                                                      | 3-112 |

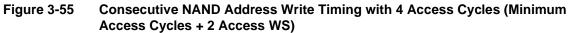

| Figure 3-56 | Consecutive NAND Data Write Timing with 3 Access Cycles                                                                    |       |

|             | (Minimum Access Cycles + 1 Access WS)                                                                                      | 3-113 |

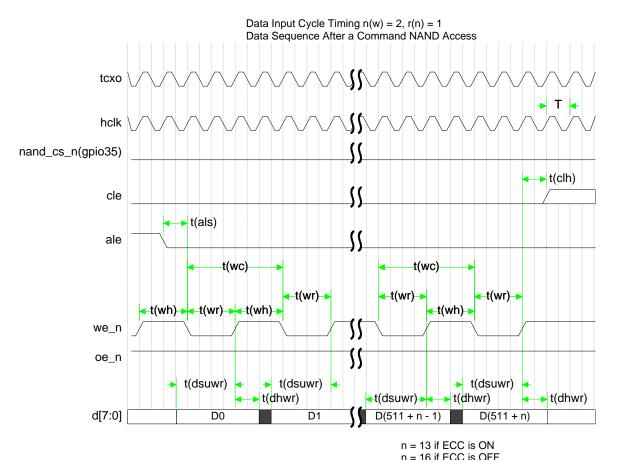

| Figure 3-57 | Consecutive NAND Command Write Timing with 4 Access Cycles                                                                 | 2 115 |

| E           | (Minimum Access Cycles + 2 Access WS)                                                                                      |       |

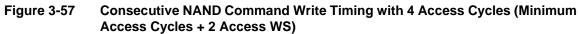

| Figure 3-58 | Consecutive NAND Data Read Timing with 3 Access Cycles<br>(Minimum Access Cycles + 1 Access WS) After Waiting for R/B_N to |       |

|             | Go High                                                                                                                    | 3-116 |

|             | ov mgn                                                                                                                     |       |

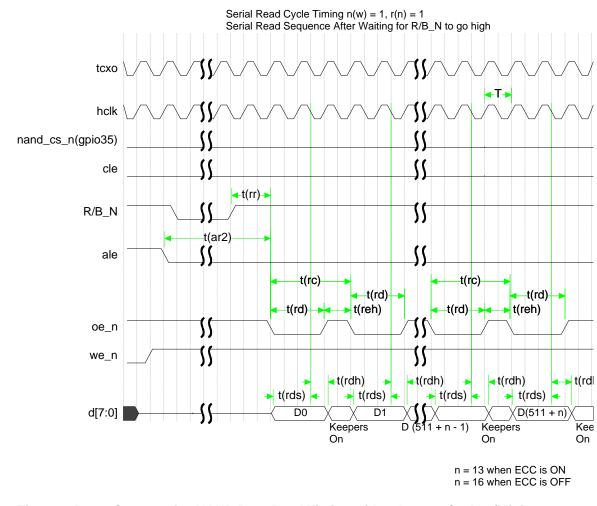

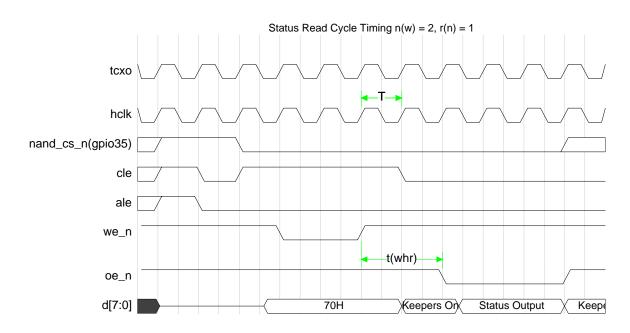

| Figure 3-59 | Continuous Status Command Sequence With 3 Access Cycles<br>(Minimum Access Cycles + 1 Access WS)   | 3-118 |

|-------------|----------------------------------------------------------------------------------------------------|-------|

| Figure 3-60 | Continuous Status Command Sequence With 4 Access Cycles<br>(Minimum Access Cycles + 2 Access WS)   | 3-119 |

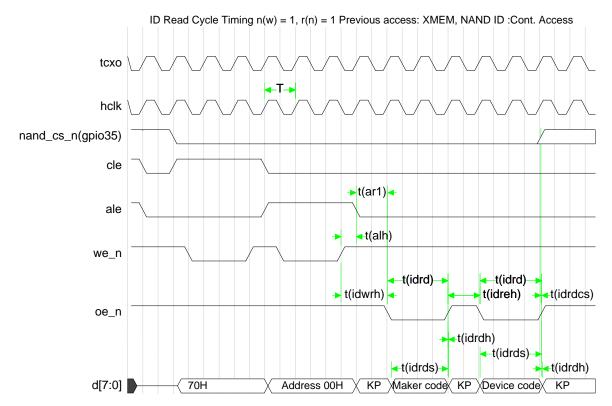

| Figure 3-61 | Continuous ID Command Sequence With First Access<br>Following an XMEM Access(0 and 1 Wait States)  |       |

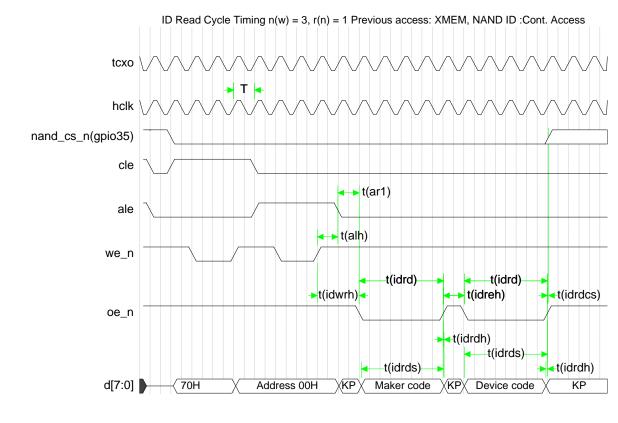

| Figure 3-62 | Continuous ID Command Sequence With First Access<br>Following an XMEM Access (2 and 3 Wait States) |       |

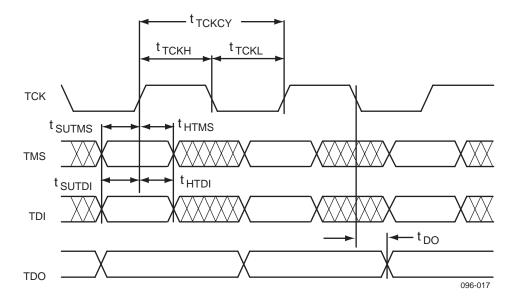

| Figure 3-63 | JTAG Interface Timing                                                                              |       |

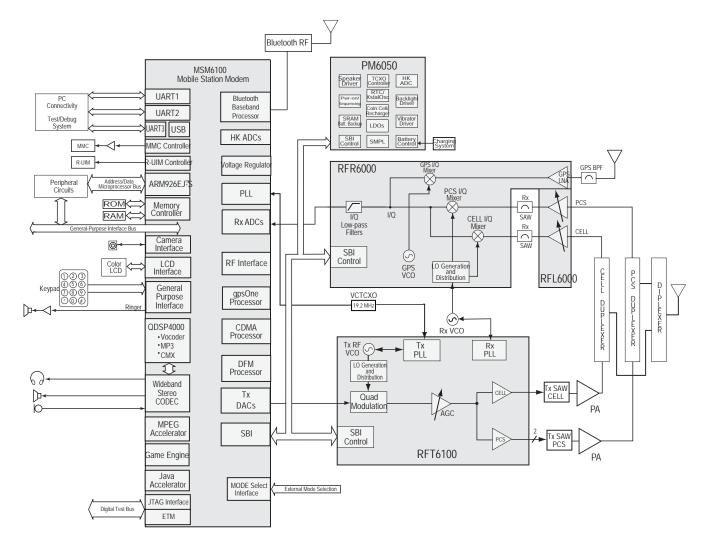

| Figure 4-1  | MSM6100 Device Functional Block Diagram                                                            |       |

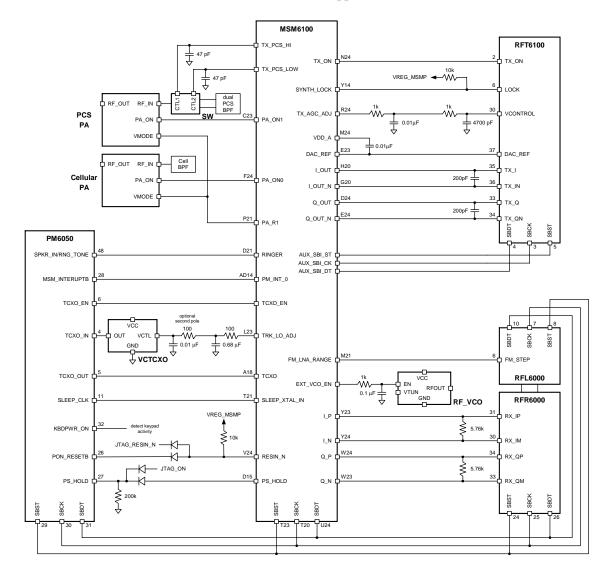

| Figure 4-2  | Interface Connections for the MSM6100 Chipset                                                      |       |

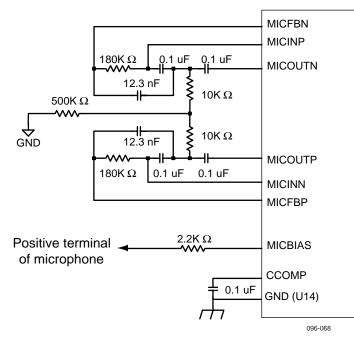

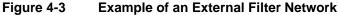

| Figure 4-3  | Example of an External Filter Network                                                              |       |

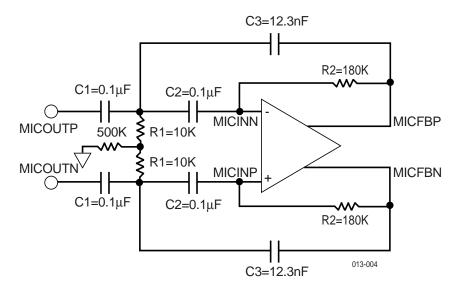

| Figure 4-4  | Equivalent Circuit for External Filter Network                                                     |       |

| Figure 4-5  | Equivalent circuit for MICAMP2                                                                     |       |

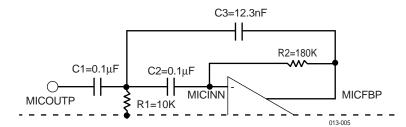

| Figure 4-6  | Slope Filter                                                                                       |       |

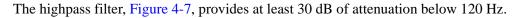

| Figure 4-7  | Highpass Filter                                                                                    |       |

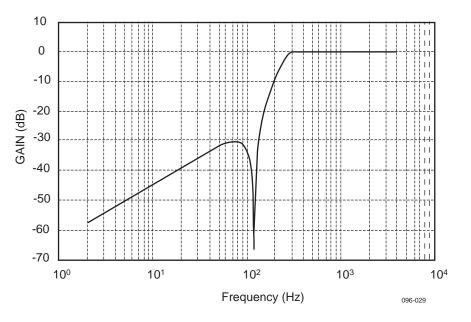

| Figure 4-8  | Typical Handset Interface                                                                          |       |

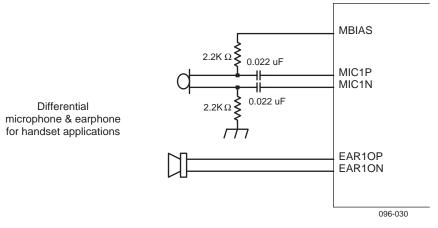

| Figure 4-9  | Typical Handset Application                                                                        |       |

| Figure 4-10 | Typical Analog Car-kit Application                                                                 |       |

| Figure 4-11 | Auxiliary/Primary PCM Interface                                                                    |       |

| Figure 4-12 | AHB System Architecture                                                                            |       |

| Figure 4-13 | MSM6100 Memory Map                                                                                 | 4-24  |

| Figure 4-14 | Fast Peripheral Bridge                                                                             | 4-26  |

| Figure 4-15 | Fast Peripheral Bus Memory Region Map                                                              | 4-27  |

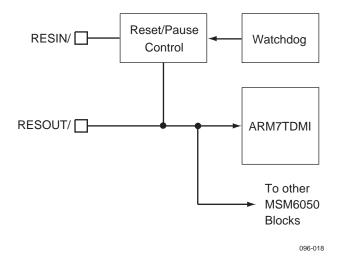

| Figure 4-16 | Reset Generation                                                                                   | 4-29  |

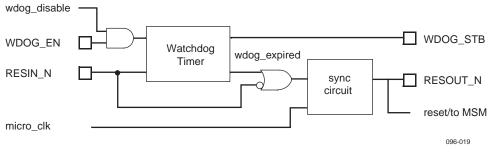

| Figure 4-17 | Watchdog Timer Configuration                                                                       |       |

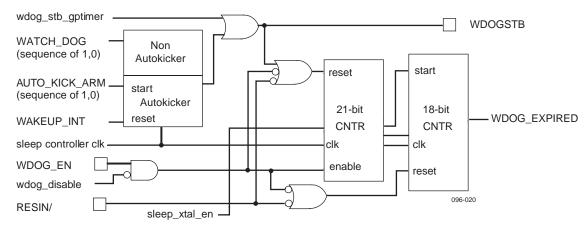

| Figure 4-18 | Watchdog Timer Block Diagram                                                                       | 4-31  |

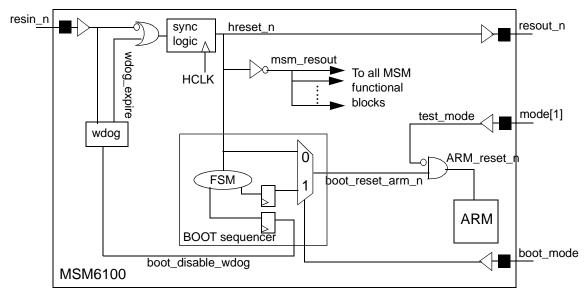

| Figure 4-19 | MSM6100 Reset Scheme                                                                               |       |

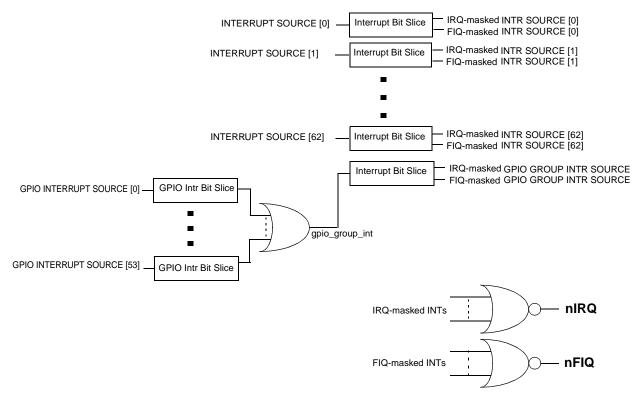

| Figure 4-20 | Interrupt Controller                                                                               | 4-33  |

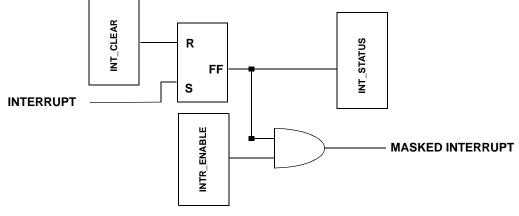

| Figure 4-21 | GPIO Group 1 Level 2 Interrupt Controller Bit Slice                                                | 4-34  |

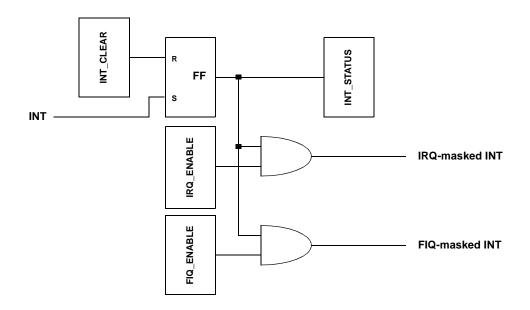

| Figure 4-22 | Level 1 Interrupt Bit Slice Design                                                                 | 4-34  |

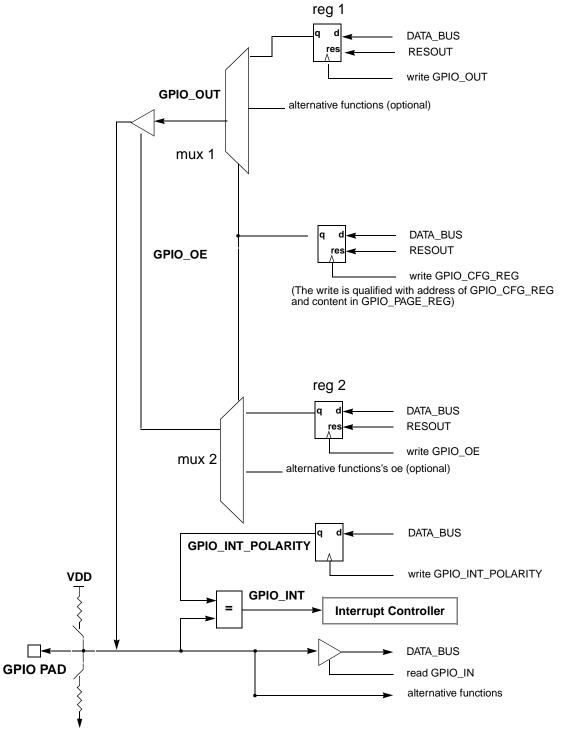

| Figure 4-23 | GPIO Structure                                                                                     |       |

| Figure 4-24 | Hardware Support for MSM Boot-up                                                                   | 4-41  |

| Figure 4-25 | EBI1 Hierarchy and Connections to External Memory Pins                                             | 4-46  |

| Figure 4-26 | Different Memory Configurations on the EBI1 Bus                                                    | 4-49  |

| Figure 4-27 | Breaking the Critical Path on the Read Data For Burst Memory Access                                | 4-61  |

| Figure 4-28 | EBI1 External Clock Generation                                                                     | 4-70  |

| Figure 4-29 | 16-bit Read, 16-bit Write, 16-bit Read Async Timing                                                | 4-72  |

| Figure 4-30 | 32-bit Read Followed by a 32-bit Write Async Timing                                                | 4-73  |

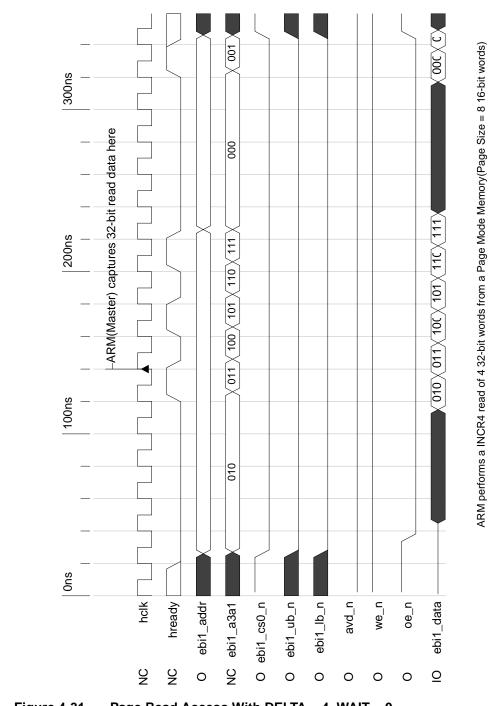

| Figure 4-31 | Page Read Access With DELTA = 4, WAIT = 0                                                          | 4-75  |

| Figure 4-32 | Page Read Access With DELTA =3, WAIT = 1                                                           | 4-76  |

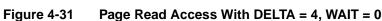

| Figure 4-33 | Page Write Access With DELTA =4, WAIT = 0                                             | 4-77  |

|-------------|---------------------------------------------------------------------------------------|-------|

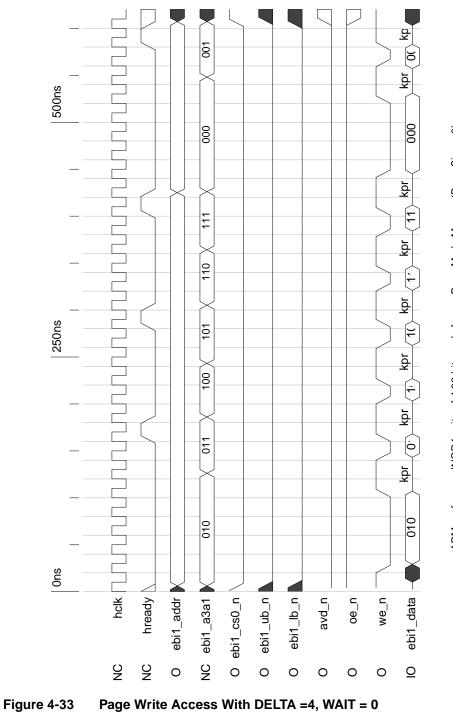

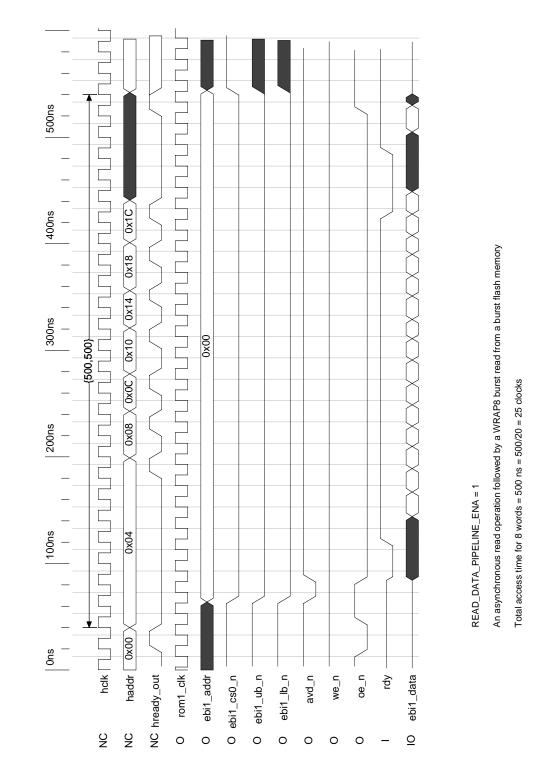

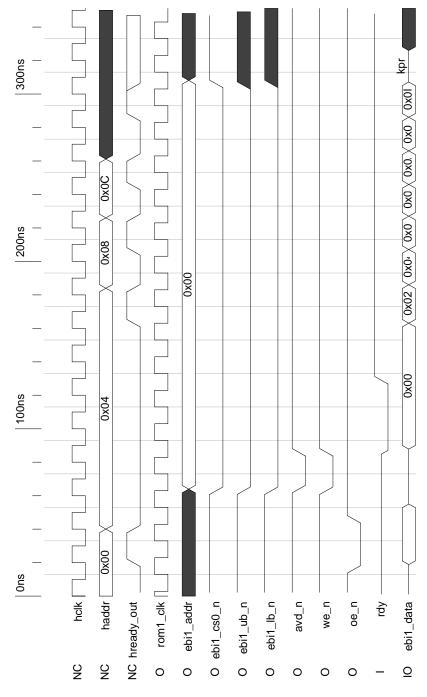

| Figure 4-34 | Burst Memory Read Timing When READ_DATA_PIPELINE_ENA = 0                              | 4-79  |

| Figure 4-35 | Burst Memory Read Timing When READ_DATA_PIPELINE_ENA = 1                              | 4-80  |

| Figure 4-36 | Burst Write Operation to a Synchronous PSRAM Device                                   | 4-81  |

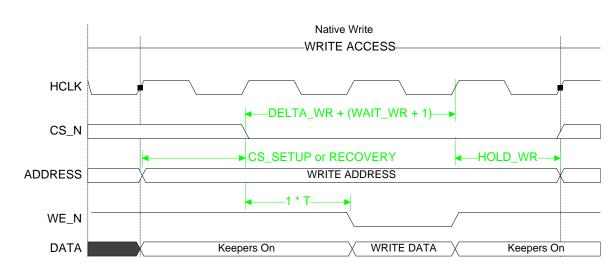

| Figure 4-37 | Native Write Timing                                                                   | 4-85  |

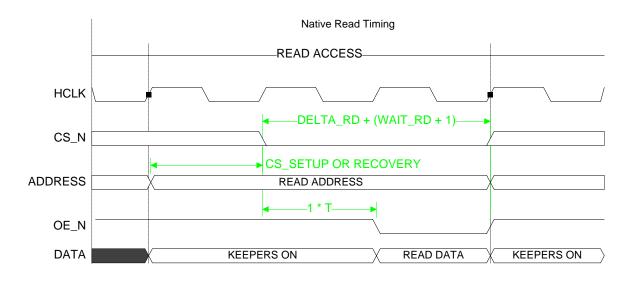

| Figure 4-38 | Native Read Timing                                                                    | 4-86  |

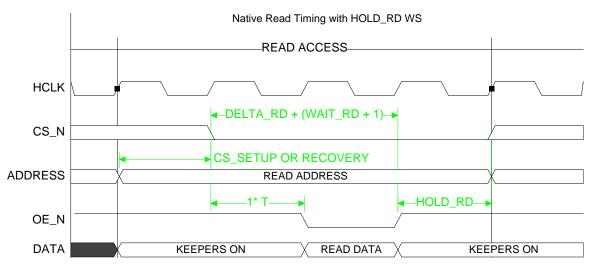

| Figure 4-39 | Native Read With HOLD_RD Wait State                                                   | 4-86  |

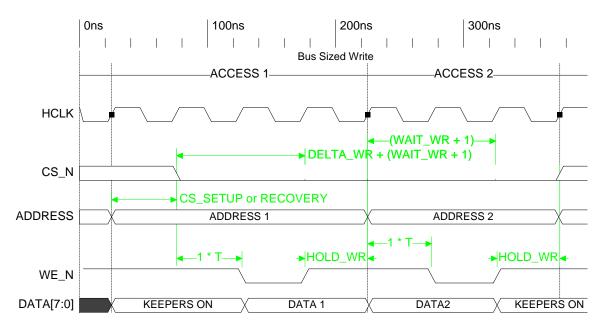

| Figure 4-40 | Bus-Sized Write Timing                                                                | 4-87  |

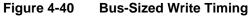

| Figure 4-41 | Bus-Sized Read Timing                                                                 | 4-87  |

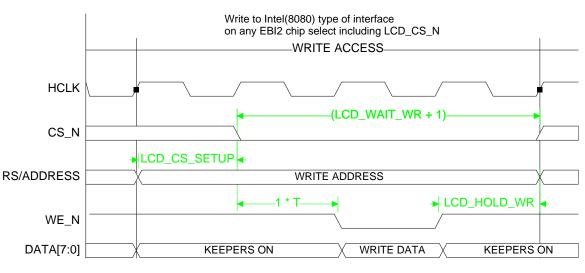

| Figure 4-42 | Timing For Parallel LCD Write to Intel(8080)-Type Interface                           | 4-89  |

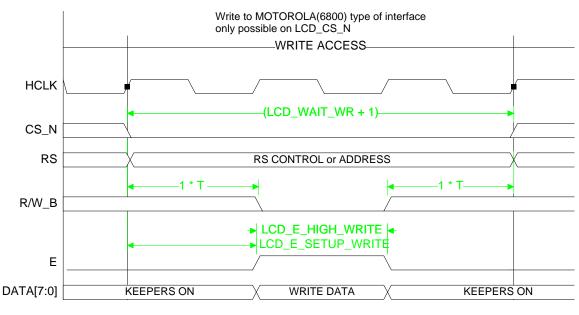

| Figure 4-43 | Timing For Parallel LCD Write to Motorola (6800)-Type Interface                       | 4-89  |

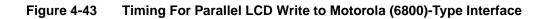

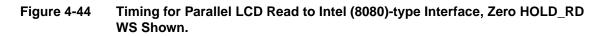

| Figure 4-44 | Timing for Parallel LCD Read to Intel (8080)-type Interface,<br>Zero HOLD_RD WS Shown | 1-90  |

| Figure 4-45 | Timing for Parallel LCD Read to Intel (8080)-Type Interface,                          |       |

| riguie 4-45 | One HOLD RD WS Shown                                                                  | 4-90  |

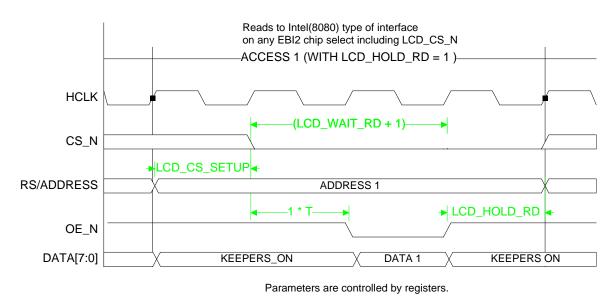

| Figure 4-46 | Timing for Parallel LCD Read to Motorola(6800)-Type interface                         |       |

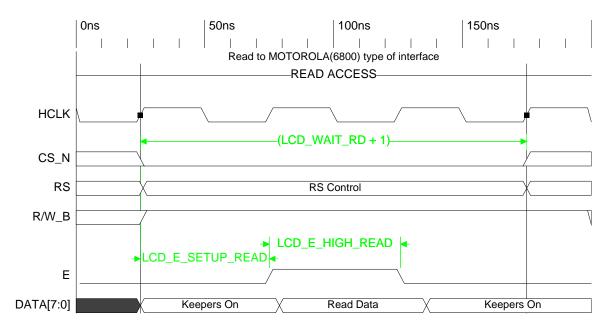

| Figure 4-47 | Timing For Parallel LCD Bus-Sized Write to Motorola (6800)-type Interfac              |       |

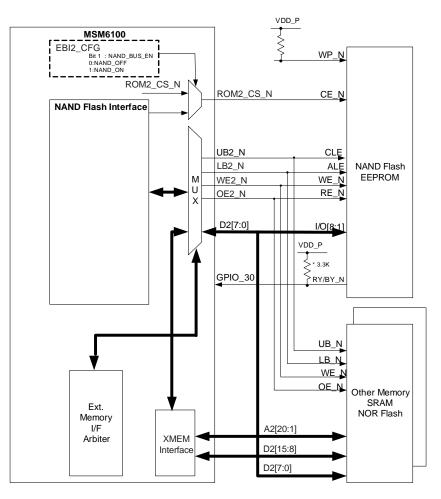

| Figure 4-48 | Interface Connection NAND Flash and MSM6100 Device                                    | 4-97  |

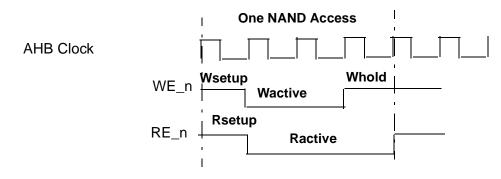

| Figure 4-49 | Basic NAND parameter                                                                  | 4-98  |

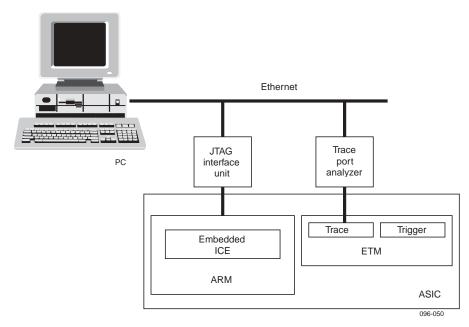

| Figure 4-50 | Example Debugging Environment                                                         | 4-101 |

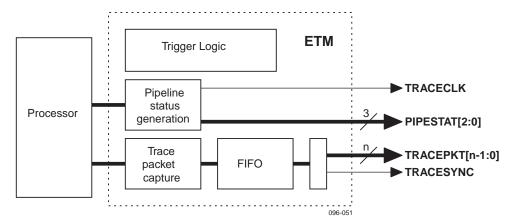

| Figure 4-51 | ETM Architecture                                                                      | 4-102 |

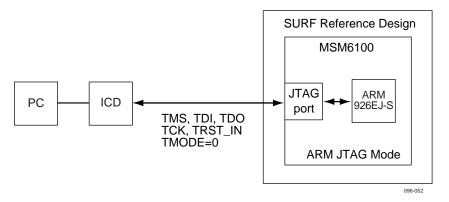

| Figure 4-52 | ARM JTAG Setup Example                                                                | 4-104 |

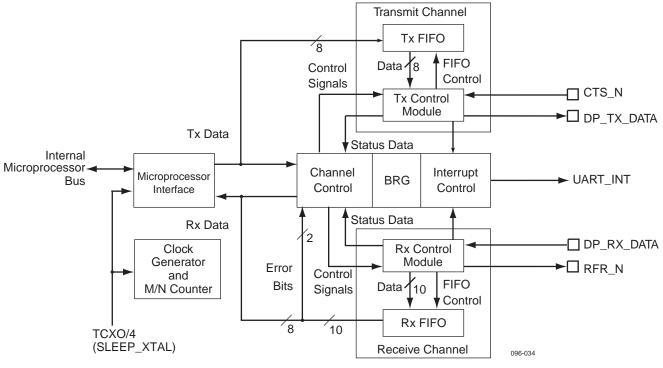

| Figure 4-53 | UART Block Diagram                                                                    | 4-105 |

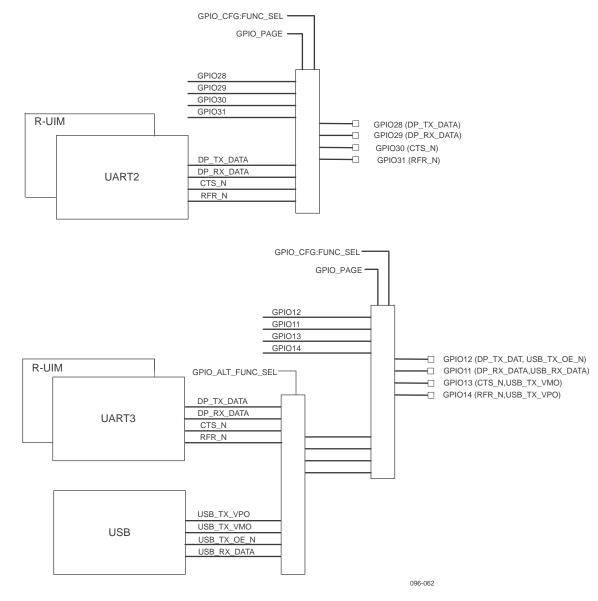

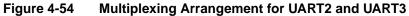

| Figure 4-54 | Multiplexing Arrangement for UART2 and UART3                                          | 4-111 |

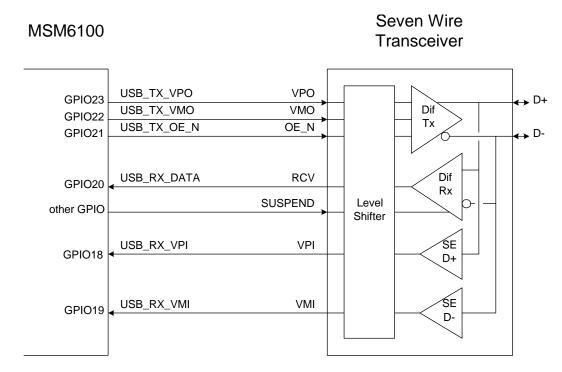

| Figure 4-55 | Seven Wire Transceiver                                                                | 4-115 |

| Figure 4-56 | Five Wire Transceiver                                                                 | 4-116 |

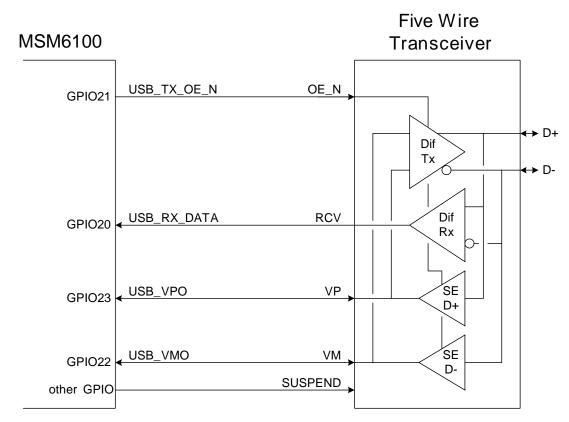

| Figure 4-57 | Three Wire Transceiver                                                                | 4-117 |

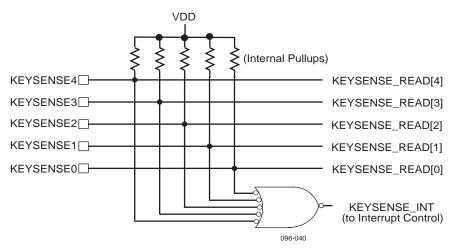

| Figure 4-58 | KEYSENSE[4:0] Circuits                                                                | 4-119 |

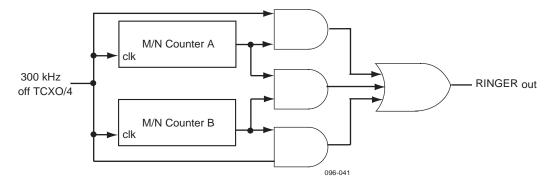

| Figure 4-59 | Ringer Generation Circuit                                                             | 4-120 |

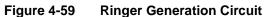

| Figure 4-60 | External Driver Circuit Example                                                       | 4-120 |

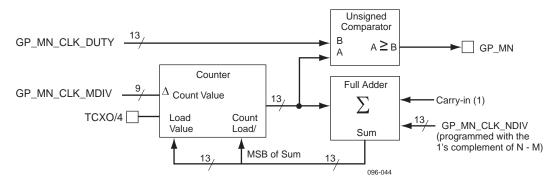

| Figure 4-61 | GP_MN Block Diagram                                                                   | 4-123 |

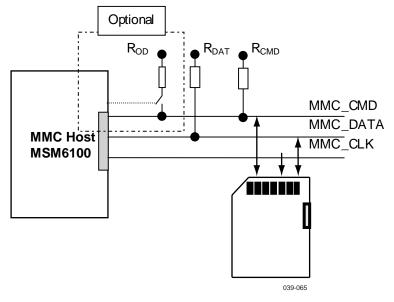

| Figure 4-62 | MMC Bus Circuitry Diagram                                                             | 4-126 |

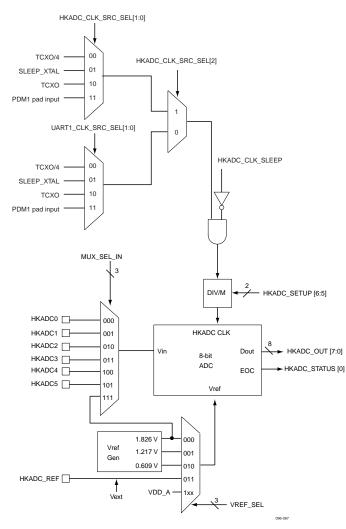

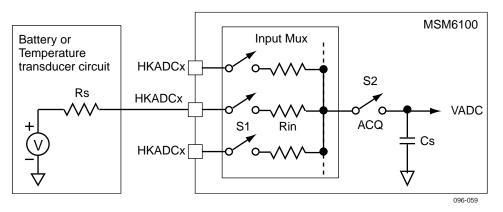

| Figure 4-63 | HKADC Configuration                                                                   | 4-128 |

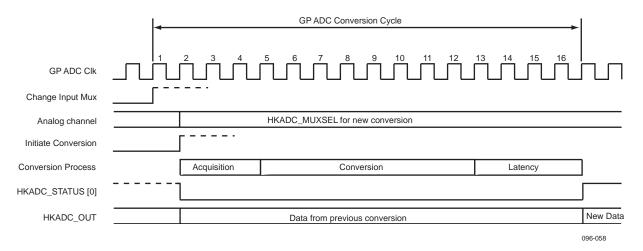

| Figure 4-64 | General HKADC Conversion Process                                                      | 4-130 |

| Figure 4-65 | Equivalent Circuits for HKADC Input and External Voltage Sources                      | 4-132 |

| Figure 4-66 | SLEEP Oscillator Circuit with Passive Crystal                                         | 4-135 |

| Figure 4-67 | USB Oscillator Circuit                                                                | 4-136 |

| Figure 4-68 | Clock Block Architecture                                                              | 4-138 |

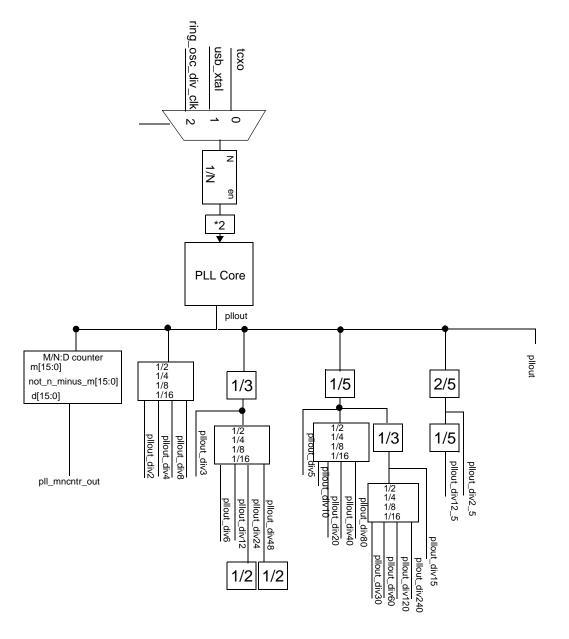

| Figure 4-69 | Clock Source Generation From PLL Core Block Diagram                                   | 4-139 |

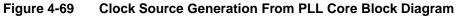

| Figure 4-70 | Clock Source Generation From CPLL Core Block Diagram                                  | 4-140 |

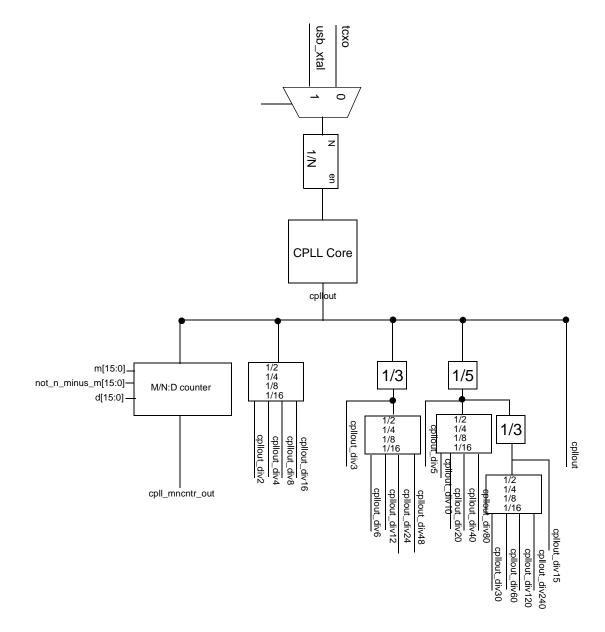

| Figure 4-71 | ARM Clock Selection.                                     | 4-143 |

|-------------|----------------------------------------------------------|-------|

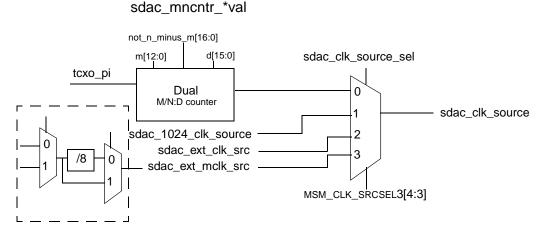

| Figure 4-72 | External Stereo Codec Clock Selection Block Diagram      |       |

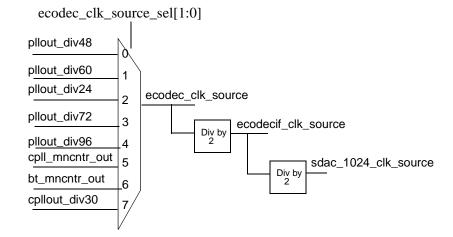

| Figure 4-73 | Ecodec Clock Selection                                   |       |

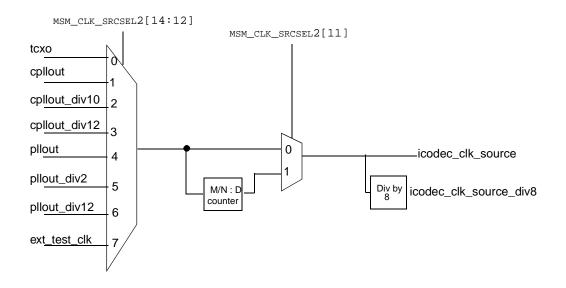

| Figure 4-74 | Internal Wide Bank Codec Clock Selection Block Diagram   |       |

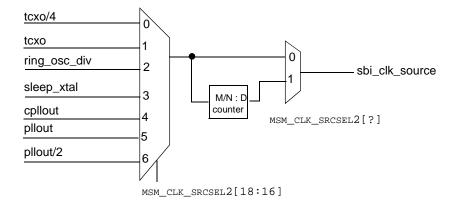

| Figure 4-75 | SBI Clock Source Selection                               | 4-146 |

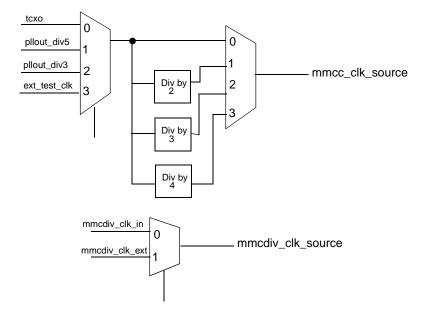

| Figure 4-76 | MMC Clock Selection                                      | 4-147 |

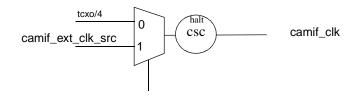

| Figure 4-77 | Camera Interface Clock Selection                         | 4-147 |

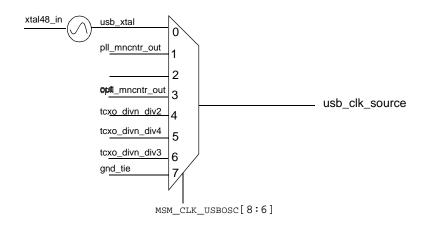

| Figure 4-78 | USB 48 MHz Clock Selection                               | 4-148 |

| Figure 4-79 | I <sup>2</sup> C Clock Selection                         | 4-148 |

| Figure 4-80 | MSM6100 Device JTAG Interface                            | 4-149 |

| Figure 4-81 | JTAG Interface Block Diagram                             | 4-150 |

| Figure 4-82 | Data Structure for Device Identification Register        |       |

| Figure 4-83 | Typical Boundary Scan Cell                               |       |

| Figure 4-84 | JTAG Connections for Using the MSM6100 BSDL              |       |

|             | Scan Chain WDOG Disabled                                 |       |

| Figure 4-85 | Connections for Using the MSM6100 ARM JTAG WDOG Disabled |       |

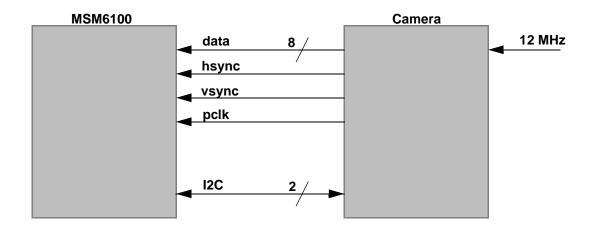

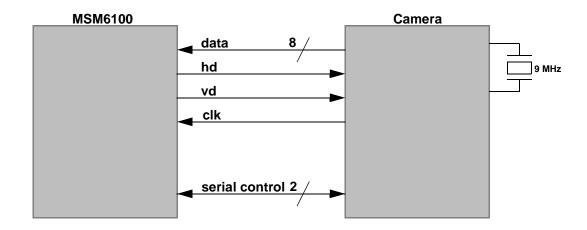

| Figure 4-86 | MSM6100 Device to Sanyo Camera Module Interconnect       |       |

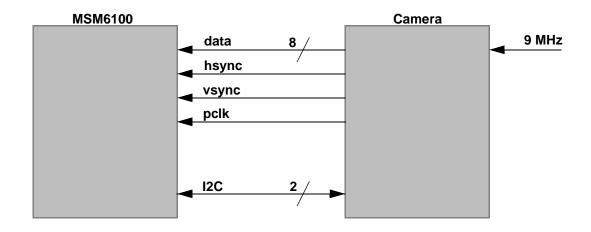

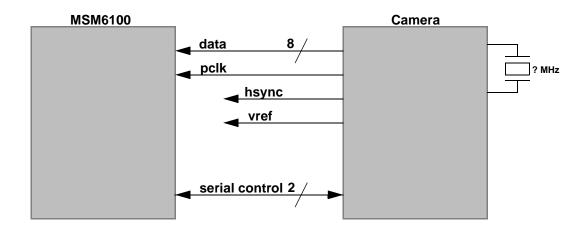

| Figure 4-87 | MSM6100 Device to Hitachi Camera Module Interconnect     | 4-161 |

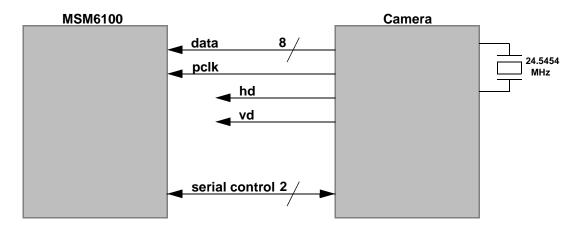

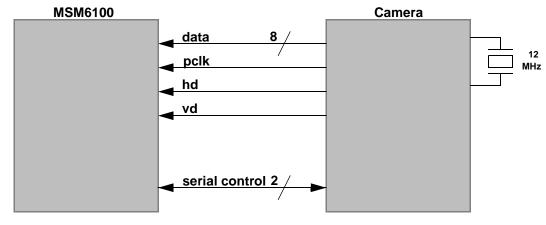

| Figure 4-88 | MSM6100 Device to Matsushita Camera Module Interconnect  |       |

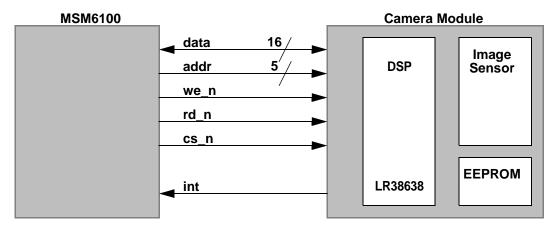

| Figure 4-89 | MSM6100 Device to Toshiba Camera Module Interconnect     | 4-163 |

| Figure 4-90 | MSM6100 Device to Sharp Image Sensor Interconnect        | 4-164 |

| Figure 4-91 | MSM to OmniVision Camera Interconnect                    |       |

| Figure 4-92 | MSM6100 Device to IC Media Camera Interconnect           | 4-165 |

| Figure 4-93 | MSM6100 Device to Sharp Camera Module Interconnect       | 4-166 |

| Figure 4-94 | MSM6100 Device to Atmel Imager                           | 4-167 |

| Figure 5-1  | Part Marking                                             |       |

|             |                                                          |       |

## Tables

| Table 1    | Usage Conventions                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------|

| Table 2    | Special Marksxxiii                                                                                                        |

| Table 3    | Revision Historyxxiv                                                                                                      |

| Table 2-1  | I/O Description (Pad Type) Parameters                                                                                     |

| Table 2-2  | Pin Names and Pinouts                                                                                                     |

| Table 2-3  | MSM6100 Pinouts (1)                                                                                                       |

| Table 2-4  | MSM6100 Pinouts (2)                                                                                                       |

| Table 2-5  | MSM6100 Pinouts (3)                                                                                                       |

| Table 3-1  | Absolute Maximum Ratings                                                                                                  |

| Table 3-2  | Recommended Operating Conditions                                                                                          |

| Table 3-3  | Thermal Resistance                                                                                                        |

| Table 3-4  | DC Characteristics (for VDD_P0 = 1.867)                                                                                   |

| Table 3-5  | DC Characteristics (for VDD_P0 = 2.60)                                                                                    |

| Table 3-6  | GPADC Performance Specification                                                                                           |

| Table 3-7  | Microphone Interface Requirements                                                                                         |

| Table 3-8  | Speaker Interface Requirements                                                                                            |

| Table 3-9  | Transmit VOICE Path Level Translation and Linearity, MIC AMP2 Enabled 3-8                                                 |

| Table 3-10 | Transmit VOICE Path Level Translation and Linearity, MIC AMP2 Bypassed 3-9                                                |

| Table 3-11 | Transmit VOICE Path Frequency Response and Image Rejection,<br>Digital Transmit Slope Filter Disabled, Mic Amp 2 Bypassed |

| Table 3-12 | Transmit VOICE Path Frequency Response and Image Rejection,                                                               |

|            | Digital Transmit Slope Filter Enabled, Mic Amp 2 Bypassed3-10                                                             |

| Table 3-13 | Transmit VOICE Path Idle Channel Noise and Distortion (8K)                                                                |

| Table 3-14 | Transmit VOICE Path Idle Channel Noise and Distortion (16K)                                                               |

| Table 3-15 | Receive VOICE Path Level Translation and Linearity, EAR_AMP1 Selected 3-12                                                |

| Table 3-16 | Receive VOICE Path Level Translation and Linearity, EAR_AMP2 Selected 3-12                                                |

| Table 3-17 | Receive VOICE Path Level Translation and Linearity, EAR_AMP3 Selected 3-13                                                |

| Table 3-18 | Receive VOICE Path Level Translation and Linearity, AUX_AMP Selected 3-13                                                 |

| Table 3-19 | Receive VOICE Path Frequency Response and Image Rejection                                                                 |

| Table 3-20 | Receive VOICE Path Idle Channel Noise and Distortion,<br>EAR_AMP1 Selected                                                |

| Table 3-21 | Receive VOICE Path Idle Channel Noise and Distortion,<br>EAR_AMP2 Selected                                                |

| Table 3-22 | Receive VOICE Path Idle Channel Noise and Distortion,                                                                     |

|            | EAR_AMP3 Selected                                                                                                         |

| Table 3-23 | Receive VOICE Path Idle Channel Noise And Distortion,                                                                     |

|            | AUX_AMP Selected                                                                                                          |

| Table 3-24 | Receive AUDIO Path Level Translation and Linearity, EAR_AMP2 Selected 3-18                                                |

| Table 3-25 | Receive AUDIO Path Level Translation and Linearity, EAR_AMP3 Selected 3-18                                                |

| Table 3-26       | Receive AUDIO Path Level Translation and Linearity, AUX_AMP (L or R)<br>Selected and Configured Single-Ended | 3-19 |

|------------------|--------------------------------------------------------------------------------------------------------------|------|

| Table 3-27       | Receive AUDIO Path Level Translation and Linearity, AUX_AMP                                                  |      |

|                  | Selected and Configured Differential                                                                         | 3-19 |

| Table 3-28       | Receive Path AUDIO Frequency Response and Image Rejection                                                    | 3-20 |

| Table 3-29       | Receive AUDIO Path Idle Channel Noise and Distortion,<br>EAR_AMP2 Selected                                   | 3-20 |

| Table 3-30       | Receive AUDIO Path Idle Channel Noise and Distortion,                                                        |      |

| Table 3-31       | EAR_AMP3 Selected<br>Receive AUDIO Path Idle Channel Noise and Distortion,                                   |      |

| Table 5-51       | AUX_AMP (R or L) Selected and Configured Single-Ended                                                        | 3-21 |

| Table 3-32       | Receive AUDIO Path Idle Channel Noise and Distortion,                                                        | 2.22 |

| <b>T</b> 11 2 22 | AUX_AMP Selected and Configured Differential                                                                 |      |

| Table 3-33       | AUXIP (Line_In_L) Input to EAR_AMP1 Output Selected                                                          |      |

| Table 3-34       | AUXIP (Line_In_L) Input to EAR_AMP2 Output Selected                                                          | 3-23 |

| Table 3-35       | AUXIP (Line_In_L) Input to AUX_AMP Output Selected<br>and Configured Differential                            | 3-23 |

| Table 3-36       | AUXIP (Line_In_L) Input to AUX_AMP Output Selected                                                           |      |

|                  | and Configured Single-Ended                                                                                  | 3-24 |

| Table 3-37       | AUXIN (Line_In_R) Input to EAR_AMP3 Output Selected                                                          | 3-24 |

| Table 3-38       | AUXIN (Line_In_R) Input to AUX_AMP Output Selected<br>and Configured Differential                            | 3-25 |

| Table 3-39       | AUXIN (Line_In_R) Input to AUX_AMP Output Selected                                                           |      |

|                  | and Configured Single-Ended                                                                                  | 3-25 |

| Table 3-40       | Power Supply Rejection and Crosstalk Attenuation                                                             | 3-26 |

| Table 3-41       | MSM6100 Device Power Supply Current                                                                          |      |

| Table 3-42       | VDD_A Power Consumption                                                                                      |      |

| Table 3-43       | Continuous Power Consumption per Voltage Rail                                                                | 3-29 |

| Table 3-44       | TCXO Timing Parameters                                                                                       |      |

| Table 3-45       | MCLK Timing Parameters                                                                                       | 3-31 |

| Table 3-46       | PCM_CODEC Timing Parameters                                                                                  |      |

| Table 3-47       | AUX_CODEC Timing Parameters                                                                                  |      |

| Table 3-48       | EBI1 Chip Select Registers Association With Pins                                                             |      |

| Table 3-49       | EBI1 Wait States                                                                                             |      |

| Table 3-50       | EBI1 Minimum Access Configuration Register Settings (Page Mode Off)                                          | 3-35 |

| Table 3-51       | EBI1 16-bit Asynchronous Write Timing                                                                        |      |

| Table 3-52       | EBI1 16-bit Asynchronous Read Timing                                                                         |      |

| Table 3-53       | EBI1 Timing Parameters Where $V_{DD} P_1 = 1.8V$                                                             |      |

| Table 3-54       | EBI1 32-bit Bus Sized Write Timing                                                                           |      |

| Table 3-55       | EBI1 32-bit Bus Sized Read Timing.                                                                           | 3-44 |

| Table 3-56       | SDRAM Controller - AC Characteristics                                                                        | 3-46 |

| Table 3-57       | Burst Memory Controller - AC Characteristics                                            | 3-48  |

|------------------|-----------------------------------------------------------------------------------------|-------|

| Table 3-58       | EBI2 Wait States                                                                        |       |

| Table 3-59       | EBI2 Timing Parameters Where V <sub>DD P2</sub> = 2.5V                                  |       |

| Table 3-60       | EBI2 Timing Parameters Where $V_{DD_P2} = 1.77 \text{ V}$                               |       |

| Table 3-61       | EBI2 Native Mode Write Timing                                                           |       |

| Table 3-62       | EBI2 Native Mode Read Timing                                                            |       |

| Table 3-63       | EBI2 Bus Sized Write Timing                                                             |       |

| Table 3-64       | EBI2 Bus Sized Read Timing                                                              |       |

| Table 3-65       | LCD Wait States                                                                         |       |

| Table 3-66       | Intel-Type Parallel LCD Timing Parameters Where $V_{DD P2} = 2.5V$                      |       |

| Table 3-67       | Intel-Type Parallel LCD Timing Parameters Where $V_{DD_P2} = 1.77V$                     |       |

| Table 3-68       | Parallel LCD Native Mode Write Timing                                                   |       |

| Table 3-69       | PLCD Native Mode Read Timing                                                            |       |

| Table 3-70       | LCD Bus Sized Write Timing                                                              |       |

| Table 3-71       | LCD Bus Sized Read Timing                                                               |       |

| Table 3-72       | Motorola-Type Parallel LCD Timing Parameters Where $V_{DD_P2} = 2.5 \text{ V}$          |       |

| Table 3-73       | Motorola-Type Parallel LCD Timing Parameters Where $V_{DD,P2} = 1.77V$ .                |       |

| Table 3-74       | LCD Interface NATIVE Read Timing, Motorola Type                                         |       |

| Table 3-75       | PLCD Interface Write Timing, Motorola Type                                              |       |

| Table 3-76       | LCD Interface BUS SIZED Read Timing, Motorola Type                                      |       |

| Table 3-77       | LCD Interface BUS SIZED Write Timing, Motorola Type                                     |       |

| Table 3-78       | NAND Wait States Description                                                            | 3-91  |

| Table 3-79       | NAND Access Timing Parameters Where $V_{DD_P2} = 2.5V$                                  | 3-92  |

| Table 3-80       | NAND Access Timing Parameters Where $V_{DD_P2} = 1.77V$                                 |       |

| Table 3-81       | NAND Command Write Timing (0 and 1 Access Wait States)                                  | 3-97  |

| Table 3-82       | NAND Command Write Timing (2 and 3 Access Wait States)                                  |       |

| Table 3-83       | NAND Address Write Timing (0 and 1 Wait States)                                         | 3-100 |

| Table 3-84       | NAND Address Write Timing (2 and 3 Access Wait States)                                  | 3-102 |

| Table 3-85       | NAND Command Data Read Timing (All Accesses)                                            | 3-104 |

| Table 3-86       | NAND Command Data Read Timing (All Accesses)                                            | 3-105 |

| Table 3-87       | NAND Data Write Timing (0 and 1 Access Wait States)                                     | 3-106 |

| Table 3-88       | NAND Data Write Timing (2 and 3 Access Wait States)                                     | 3-108 |

| Table 3-89       | NAND Memory Data Read Timing (All Accesses)                                             | 3-109 |

| Table 3-90       | Consecutive NAND Address Write Timing (0 and 1 Wait States)                             |       |

|                  | after a NAND Command Access                                                             | 3-111 |

| Table 3-91       | Consecutive NAND Address Write Timing (2 and 3 Wait States)                             | 0.110 |

| <b>T</b> 11 2 02 | after a NAND Command Access                                                             | 3-112 |

| Table 3-92       | Consecutive NAND Data Write Timing (0 and 1 Wait States)<br>after a NAND Address Access | 3-114 |

|                  |                                                                                         |       |

| Table 3-93              | Consecutive NAND Data Write Timing (2 and 3 Wait States)<br>after a NAND Address Access. | 3-115 |

|-------------------------|------------------------------------------------------------------------------------------|-------|

| Table 3-94              | Consecutive NAND Data Read Timing (All Wait States)                                      |       |

| 10010 5 74              | After Waiting for R/B_N to Go High                                                       |       |

| Table 3-95              | Continuous Status Command Sequence With First Access                                     |       |

|                         | Following an XMEM Access (0 and 1 Wait States)                                           |       |

| Table 3-96              | Continuous Status Command Sequence With First Access                                     |       |

|                         | Following an XMEM Access (2 and 3 Wait States)                                           |       |

| Table 3-97              | Continuous ID Command Sequence With First Access                                         |       |

|                         | Following an XMEM Access (0 and 1 Wait States)                                           |       |

| Table 3-98              | Continuous ID Command Sequence With First Access                                         | 2,100 |

| <b>T</b> 11 <b>2</b> 00 | Following an XMEM Access (2 and 3 Wait States)                                           |       |

| Table 3-99              | JTAG Interface Timing                                                                    |       |

| Table 4-1               | ARM Burst Transfer Support                                                               |       |

| Table 4-2               | MSM6100 Decoder HSEL Signals Description                                                 |       |

| Table 4-3               | Pin Requirements                                                                         |       |

| Table 4-4               | Memories Supported on EBI1 by the Two Memory Controllers                                 |       |

| Table 4-5               | Supported EBI1 Memory Configurations                                                     |       |

| Table 4-6               | Register Names Associated With the EBI1 Chip Selects                                     |       |

| Table 4-7               | EBI2 Chip Selects                                                                        |       |

| Table 4-8               | Access Types by Chip Select                                                              |       |

| Table 4-9               | EBI2 Priority Options                                                                    |       |

| Table 4-10              | EBI2 XMEM CFG 0 Registers                                                                |       |

| Table 4-11              | LCD_CFG0 Register                                                                        |       |

| Table 4-12              | LCD_CFG1 Register                                                                        |       |

| Table 4-13              | LCD_CFG0 Register                                                                        |       |

| Table 4-14              | LCD_CFG1 Register                                                                        |       |

| Table 4-15              | NAND Flash Controller Commands                                                           |       |

| Table 4-16              | Command Sequences Generated by Writes to the                                             |       |

|                         | NAND_FLASH_CMD Register                                                                  |       |

| Table 4-17              | Example Data Assignment                                                                  |       |

| Table 4-18              | Chip Select Configuration Registers for EBI2                                             |       |

| <b></b>                 | External Memory Controller (LCD)                                                         |       |

| Table 4-19              | Wait State Table for Writes                                                              |       |

| Table 4-20              | Wait State Table for Reads                                                               |       |

| Table 4-21              | Operating Modes                                                                          |       |

| Table 4-22              | GPIO Pins Used in ETM Mode                                                               |       |

| Table 4-23              | Clock Select Register Bit Rates (Based on 1.8432 MHz Input)                              |       |

| Table 4-24              | Clock Select Register Bit Rates (Based on 7.3728 MHz Input)                              |       |

| Table 4-25              | GPIO Pins (UART2)                                                                        |       |

| Table 4-26              | GPIO Pins (UART3)                                                                        |       |

| Table 4-27 | Transceiver Connections                                 |       |

|------------|---------------------------------------------------------|-------|

| Table 4-28 | USB Endpoint Configurations                             |       |

| Table 4-29 | Standard DTMF Frequencies and Ringer Programming Values | 4-121 |

| Table 4-30 | Keypad Frequencies                                      |       |

| Table 4-31 | Using GP_MN as a Digital Output                         |       |

| Table 4-32 | I2C Pins                                                |       |

| Table 4-33 | I2S Pins                                                |       |

| Table 4-34 | MSM6100 ADC Transfer Function                           |       |

| Table 4-35 | ADC Timing for TCXO/4 Clock Source                      | 4-131 |

| Table 4-36 | ADC Timing for TCXO Clock Source                        |       |

| Table 4-37 | Recommended Rs Maximum Values                           |       |

| Table 4-38 | SLEEP Oscillator Inverter Relative Gain Settings        |       |

| Table 4-39 | Descriptions of Clock Origins                           | 4-141 |

| Table 4-40 | MSM6100 Device Clock Regimes                            | 4-141 |

| Table 4-41 | Boundary Scan Cell Control Signals                      | 4-154 |

| Table 5-1  | Marking Descriptions                                    |       |

|            |                                                         |       |

## **About this Technical Manual**

This manual provides hardware interface and programming information for the MSM6100 Mobile Station Modem. The manual is divided into the following chapters:

| Chapter 1:<br>Introduction                 | This chapter introduces users to the MSM6100 device's basic features and functions.                                                                                                   |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2:<br>Pin Descriptions             | This chapter lists each MSM6100 device pin and its function within the device. The pinout for the 341-ball CSP package is listed by functional grouping.                              |

| Chapter 3:<br>Electrical<br>Specifications | This chapter specifies the recommended operating conditions, DC voltage characteristics, I/O timing, and power estimations for the MSM6100 device. Timing diagrams are also included. |

| Chapter 4:<br>Interface<br>Descriptions    | This chapter details each subsystem or block within the MSM6100 device<br>and how the subsystem or block interfaces to external peripherals.                                          |

| Chapter 5:<br>Mechanical<br>Dimensions     | This chapter provides package dimensions and land pattern for the 341-ball CSP.                                                                                                       |

#### Usage Conventions

The following table defines terms commonly used throughout this manual.

| ADC A<br>AEC A | Definition         Audio Automatic Gain Control         Analog-to-digital converter         Acoustic Echo Cancellation         Automatic Gain Control         Advanced Mobile Phone System (analog IS-95) |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ADC A<br>AEC A | Analog-to-digital converter<br>Acoustic Echo Cancellation<br>Automatic Gain Control                                                                                                                       |  |

| AEC A          | Acoustic Echo Cancellation<br>Automatic Gain Control                                                                                                                                                      |  |

| -              | Automatic Gain Control                                                                                                                                                                                    |  |

| AGC A          |                                                                                                                                                                                                           |  |

|                | Advanced Mobile Phone System (analog IS-95)                                                                                                                                                               |  |

| AMPS A         |                                                                                                                                                                                                           |  |

| ASIC A         | Application Specific Integrated Circuit                                                                                                                                                                   |  |

| BER E          | Bit error rate                                                                                                                                                                                            |  |

| BPF E          | Bandpass Filter                                                                                                                                                                                           |  |

| Bps E          | Bits per second                                                                                                                                                                                           |  |

| CAGC C         | CDMA AGC                                                                                                                                                                                                  |  |

| CDMA C         | Code-Division Multiple Access                                                                                                                                                                             |  |

| CELP C         | Code Excited Linear Prediction                                                                                                                                                                            |  |

| CMX™ C         | Compact Media Extension. Trademarked by QUALCOMM.                                                                                                                                                         |  |

| CODEC C        | Coder-Decoder                                                                                                                                                                                             |  |

| CR C           | Command Register                                                                                                                                                                                          |  |

| CSM C          | Cell Site Modem                                                                                                                                                                                           |  |

| CSP C          | Chip Scale Package                                                                                                                                                                                        |  |

| CRC C          | Cyclic Redundancy Code                                                                                                                                                                                    |  |

| DBR E          | Data Burst Randomization                                                                                                                                                                                  |  |

| DFM C          | Digital Frequency Modulation                                                                                                                                                                              |  |

| DSP C          | Digital Signal Processor                                                                                                                                                                                  |  |

| DTMF C         | Dual-Tone Multiple-Frequency                                                                                                                                                                              |  |

| EBI E          | External Bus Interface                                                                                                                                                                                    |  |

| ESEC E         | Ear Seal Echo Cancellation                                                                                                                                                                                |  |

| ETM E          | Embedded Trace Macrocell                                                                                                                                                                                  |  |

| EVRC E         | Enhanced Variable Rate CODEC                                                                                                                                                                              |  |

| F-QPCH F       | Forward Quick Paging Channel                                                                                                                                                                              |  |

Table 1Usage Conventions

|                    | Usage Conventions (Continued)                                                                                                                                                  |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Term               | Definition                                                                                                                                                                     |  |

| FIFO               | First-In First-Out                                                                                                                                                             |  |

| FIR                | Finite Impulse Response                                                                                                                                                        |  |

| FM                 | Frequency Modulation                                                                                                                                                           |  |

| FOCC               | Forward Control Channel                                                                                                                                                        |  |

| FVC                | Forward Voice Channel                                                                                                                                                          |  |

| GPIO               | General-purpose Input/Output                                                                                                                                                   |  |

| HPF                | Highpass Filter                                                                                                                                                                |  |

| ICD                | In-Circuit Debugger                                                                                                                                                            |  |

| ICE                | In-Circuit Emulation, or In-circuit emulator                                                                                                                                   |  |

| IF                 | Intermediate Frequency                                                                                                                                                         |  |

| IR                 | Instruction Register                                                                                                                                                           |  |

| JPEG               | Joint Photographic Experts Group                                                                                                                                               |  |

| JTAG               | Joint Test Action Group (ANSI/ICEEE Std. 1149.1–1990)                                                                                                                          |  |

| kbps               | Kilobits per Second                                                                                                                                                            |  |

| LCD                | Liquid Crystal Display                                                                                                                                                         |  |

| LNA                | Low Noise Amplifier                                                                                                                                                            |  |

| LPF                | Lowpass Filter                                                                                                                                                                 |  |

| LSByte or<br>LSBit | Defines whether the LSB is the least significant bit or least significant byte. All instances of LSB used in this manual are assumed to be LSByte, unless otherwise specified. |  |

| MMC                | Multimedia Card                                                                                                                                                                |  |

| MPEG               | Moving Pictures Experts Group                                                                                                                                                  |  |

| MSByte or<br>MSBit | Defines whether the MSB is the most significant bit or most significant byte. All instances of MSB used in this manual are assumed to be MSByte, unless otherwise specified.   |  |

| MSM™               | Mobile Station Modem. Trademarked by QUALCOMM.                                                                                                                                 |  |

| NMI                | Non-maskable Interrupt                                                                                                                                                         |  |

| NS                 | Noise Suppression                                                                                                                                                              |  |

| PA                 | Power Amplifier                                                                                                                                                                |  |

| PCM                | Pulse Coded Modulation                                                                                                                                                         |  |

| PDE                | Position Determination Entity                                                                                                                                                  |  |

| PCS                | Personal Communications Service                                                                                                                                                |  |

Table 1

Usage Conventions (Continued)

| Term  | Definition                                  |  |  |  |

|-------|---------------------------------------------|--|--|--|

| PDM   | Pulse Density Modulation                    |  |  |  |

| PN    | Pseudo-Random Noise                         |  |  |  |

| PNG   | Portable Network Graphics                   |  |  |  |

| PSRAM | Pseudo Static Random Access Memory          |  |  |  |

| QCELP | QUALCOMM Code Excited Linear Prediction     |  |  |  |

| RC    | Resistance-Capacitance                      |  |  |  |

| RF    | Radio Frequency                             |  |  |  |

| RLP   | Radio Link Protocol                         |  |  |  |

| RRM   | Reduced Rate Mode                           |  |  |  |

| RSSI  | Receive Signal Strength Indicator           |  |  |  |

| RVC   | Reverse Voice Channel                       |  |  |  |

| Rx    | Receive                                     |  |  |  |

| SAT   | Supervisory Audio Tone                      |  |  |  |

| SCH   | Supplemental Channel                        |  |  |  |

| SDRAM | Synchronous Dynamic Random Access Memory    |  |  |  |

| SMV   | Selectable Mode Vocoder                     |  |  |  |

| SNR   | Signal to Noise Ratio                       |  |  |  |

| Sps   | Symbols Per Second (or Samples Per Second)  |  |  |  |

| SER   | Symbol Error Rate                           |  |  |  |

| TAP   | Test Access Port                            |  |  |  |

| тсхо  | Temperature-Controlled Crystal Oscillator   |  |  |  |

| Тх    | Transmit                                    |  |  |  |

| UART  | Universal Asynchronous Receiver Transmitter |  |  |  |

| UHF   | Ultra High Frequency                        |  |  |  |

| WBD   | Wide Band Data                              |  |  |  |

| ZIF   | Zero Intermediate Frequency                 |  |  |  |

#### Table 1 Usage Conventions (Continued)

#### **Special Marks**

The following table defines special marks used in this manual.

#### Table 2Special Marks

| Mark   | Definition                                                                                                                                                                                                                                                                     |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| []     | Brackets ([]) sometimes follow a pin, register, or bit name. These brackets enclose a range of numbers. For example, GPIO_INT [7:0] may indicate a range that is 8 bits in length, or DATA[7:0] may refer to all eight DATA pins.                                              |  |  |

| _N     | A suffix of "_N" indicates an active low signal. For example, RESIN_N.                                                                                                                                                                                                         |  |  |

| 0x0000 | Hexadecimal numbers are identified with an x in the number, for example, 0x0000. All numbers are decimal (base 10) unless otherwise specified. Non-obvious binary numbers have the term "binary" enclosed in parentheses at the end of the number, for example, 0011 (binary). |  |  |

| I      | A vertical bar in the outside margin of the page indicates a change or revision has occurred since the last release of the document.                                                                                                                                           |  |  |

#### **Revision History**

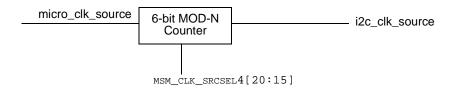

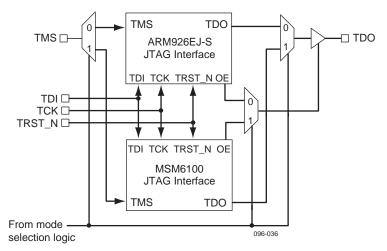

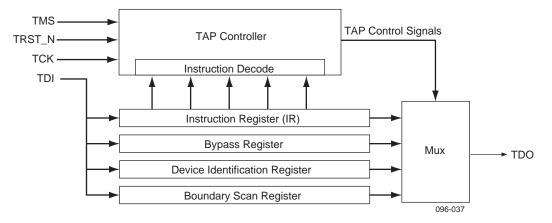

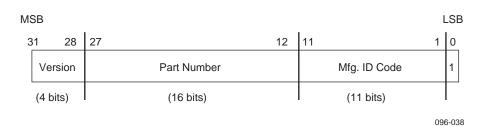

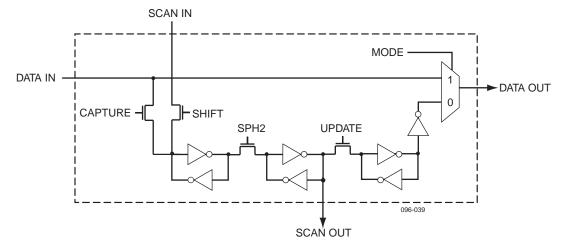

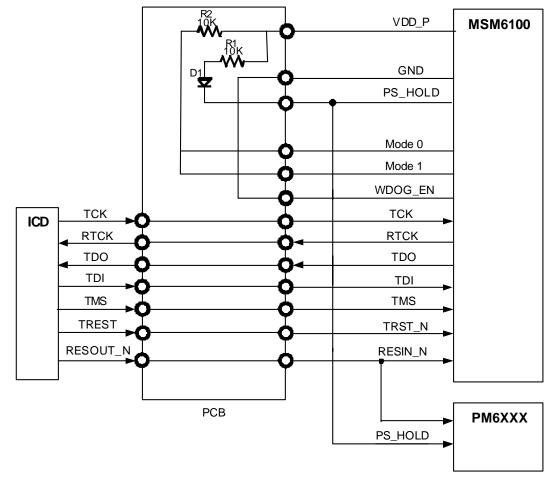

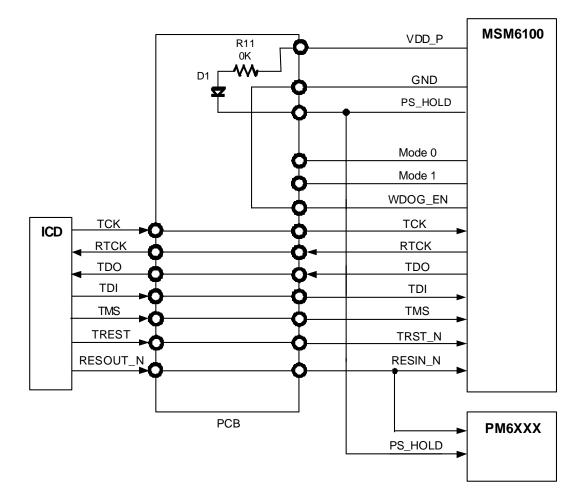

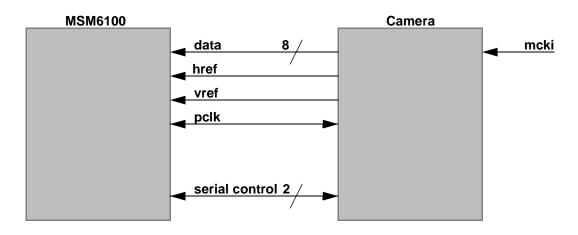

| Revision | Date            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |