# **Theory of Operation**

### Introduction

Motorola A630 telephone is small and lightweight global system for mobile communications (GSM) general packet radio service (GPRS) wireless application protocol (WAP)-enabled mobile phones. The A630 incorporates a new user interface (UI) for easier operation, allows short message service (SMS) text messaging, and includes personal information manager (PIM) functionality. The supported bands for phone are listed below.

• GSM 850/EGSM900/GSM1800/GSM1900 MHz GPRS (Class 10)

A630 telephone supports GPRS and SMS in addition to traditional circuit switched transport technologies.

A630 telephone has a clam form factor (communicator style). It has an externally viewable 96 x 48 pixel display for caller identification, date/time and external UI and external keypad for basic UI operations (menu browsing, phonebook, profiles etc.). When flip is open an internal 176 x 220 pixel display is visible. The speaker and the camera are both located in the flip. The bottom part of the clam contains the QWERTY keypad for advanced messaging, transceiver printed wired board (PWB), microphone, flex connection, external accessory connector (CE bus), smart button and volume buttons. The standard Lithium Ion (Li Ion) battery fits behind a removable back cover. Capacity of the standard battery is 780 mAh. The phone accepts 3V mini subscriber identity module (SIM) card which fit into the SIM holder underneath the battery. The antenna is internal triple band antenna. There are two antenna versions, one for US market (850/1800/1900 MHz) and one for Europe market (900/1800/1900 MHz). Inexpensive direct connection to a computer or handheld device via RS232 or USB for data and fax calls, and for synchronizing phonebook entries with TrueSync® software, can be accomplished by using the optional data cable and soft modem.

A630 telephone uses advanced, self-contained, sealed, custom integrated circuits to perform the complex functions required for GSM GPRS communication. Aside from the space and weight advantage, microcircuits enhance basic reliability, simplify maintenance, and provide a wide variety of operational functions.

## Eagle 9G

Features available in this telephone include:

- GSM 850/900/1800/1900 MHz GPRS Class 10 (separate antenna versions for 850/1800/ 1900 and 900/1800/1900 MHz)

- Built in VGA Camera (640x480 pixels)

- 65K TFT Active Color Display

- External CLI Display (Transflective Reversed)

- Polyphonic Speaker

- Speaker Phone

- Bluetooth<sup>TM</sup>

- Video Clip Playback

- 5MB User Memory

# Eagle 9G

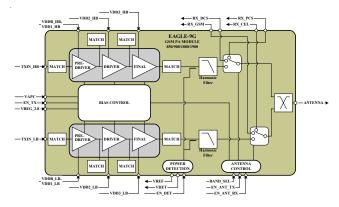

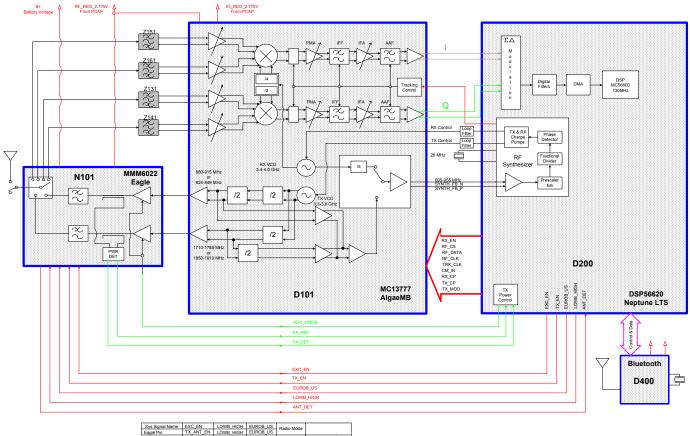

EAGLE-9G\_is a 2W TX front end-module for quad, tri-, and dual-band GSM handset applications. It is compatible with GSM/GPRS operating modes. Power amplification, power coupling, power detection, low pass filtering, and antenna switching functions are integrated to simplify radio front-end design requirements. Output power is controlled through a single analog voltage pin. Transmit/receive path and enable functions are controlled through 0/2.75V logic inputs.

# Algae MB

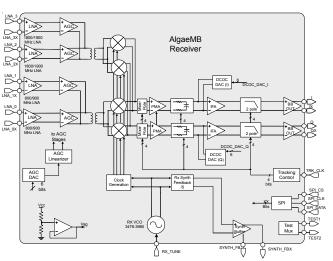

The AlgaeMB IC is a quad-band RF IC, designed in the CDR1BiCMOS process with the SiGe, MIM, and thick copper metal options.

The receiver block diagram is shown in Figure 4-3. Four LNAs are provided to eliminate the need for external RF switches when using the available receiver frequency bands. On the IC two hi band LNAs (DCS and PCS bands) and two low band LNAs (GSM850 and EGSM) are grouped together to share the same transformers at the output. The LNAs have differential inputs which will be connected in pairs as hiband-lowband (EGSM+DCS, GSM850+PCS) to the receive SAW filter with single ended inputs and dual differential outputs for each band. The groupings of LNAs at the inputs are driven by the market requirements. The LNAs drive AGC current steering stages that feed integrated transformer matching networks. The transformer drives the quadrature mixers that convert the RF signal to baseband quadrature I and Q. The output of the mixer connects directly to the post-mixer amplifier. Large integrated capacitors are used to provide a low-frequency, low-pass corner at the output of

## Figure 4-3 Algae MB Receiver

A630

the mixer. The signal then passes through baseband amplification and anti-aliasing filtering before going to an off-chip analog-to-digital converter on Neptune LTE.

The LO signal is provided by a fully integrated VCO that drives either a divide-by-two or divide-by-four quadrature generator. In addition, a divide-by-3or5 circuit is used to feed back the LO signal to the synthesizer. The divide-by-3or5 circuit drives a differential output stage that provides the appropriate power level to the synthesizer. This output stage is shared with the TX path and provides the synthesizer feedback signal in both transmit and receive.

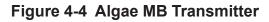

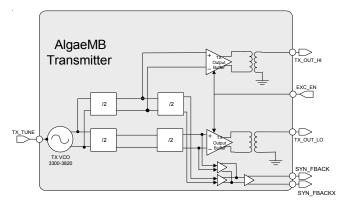

Figure 4-4 shows the block diagram for the transmitter section of the Algae MB IC. An integrated VCO is used for the transmit path. Due to the stringent sideband noise requirements for GSM, extreme care must be taken in the design of the VCO and buffer stages. A single VCO is used for transmit. A low noise floor divide-by-2 stage drives the high band output. The low band output is driven by a divide-by-4 stage.

Two transmit output stages are provided. Both stages have integrated output matches in order to reduce the required number of discrete components. The integrated matches are implemented as differential to single-ended transformers. The transmit signal is fed back to the synthesizer through a differential output stage that is shared with the receiver.

## **Power Distribution**

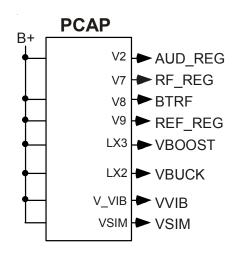

The PCAP IC provides voltage regulation. Multiple regulators are used to provide better isolation between sensitive load circuitry and noisy circuitry. The regulators and their load circuitry are listed below.

#### Figure 4-5 PCAP Regulators - 1

Figure 4-6 PCAP Regulators - 2

#### **Clock Generation**

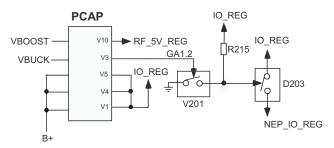

Vbuck, 1.875V +/- 4% Sources Neptune Core Vboost 5.6V +/- 5% Source for V10 & QWERTY keypad EL backlight V1 = I/O REG, 2.875V +/- 3%, Neptune I/O Reg 2.875 + 2/-4%Sources Neptune I/O, ATI Graphics Accel I/ O Ring, Camera, SPI interfaces V3 = GA1.2, Starts at 1.575V then SW selected to 1.275 +/-3% Sources ATI Graphics Accelerator core V4/V5 = tied to V1, programmed to OFF, but source internal PCAP circuitry V6 = NCV7 = RF REG, 2.875V + -3%Sources Algae and Support circuitry. V8 = BTRF, 1.875V +/- 3% Sources Blue Tooth circuitry V9 = REF REG, 1.575 V +/- 3% RTC and Neptune reference V10 = RF 5V REG, 5V +/- 3% Sources Neptune TX/RX Charge pump

## **Clock Generation**

PCAP can generate a 32kHz clock either from an internal RC Oscillator or an external crystal. The internal RC oscillator doesn't provide the stability that the Neptune requires for optimal performance; therefore, an external 32.768kHz crystal is used.

The PGM2 pin of PCAP is tied to LCELL BYP, to prevent the internal RC oscillator from being routed to the 32kHz pin under any circumstances. The 32kHz oscillator will run at all times. It is powered by LCELL, a coincell battery that is also used to maintain the real time clock. The phone will only power up when the 32kHz becomes stable.

#### PCAP Debounce Logic RC Oscillator 8x PLL Control Logic Clock Detect Xtal1 ⊢ 32kHz 32kHz Oscillato 32out en

Figure 4-7 PCAP 32kHz Clock

# PCAP TX Audio

Xtal2

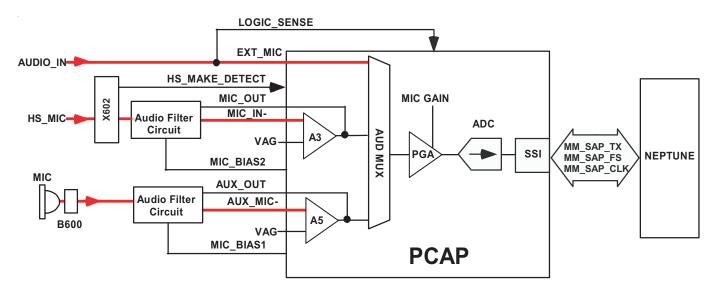

The mobile phone supports three microphone input paths identified as Internal Microphone (AUX MIC-), Headset Microphone (MICIN-), and External Microphone (EXT MIC). These three inputs are single-ended with respect to VAG. The proper Microphone path is selected by the MUX controller and path gain is programmable at the PGA.

The Internal Microphone is a single ended hand-assembled part with spring contacts. Following the Internal microphone path, the microphone is biased by R448 to provide a MIC BIAS of 2.0V from pin MIC BIAS1 of PCAP. C457 is connected to MIC BIAS1 and MB CAP1 pin on PCAP to bypass the gain from the VAG to MIC BIAS1, which keeps the noise balanced. From there, the signal is routed through C460, R450 to AUX MIC- pin on PCAP, which is the input to the A5 amplifier. The microphone path is tapped off by R451 to connect the AUX OUT pin of PCAP, which is the output of the A5 amplifier.

The headset microphone path is biased through R447,

#### PCAP RX Audio

which is connected to pin MIC\_BIAS2 on PCAP and bypassed with C456 connected to pin MB\_CAP2. From here the signal is routed through C451, R444, and R446 to MIC\_IN- pin on PCAP, which is the input to the A3 Amplifier. The Microphone path is tapped off by R445 to connect the MIC\_OUT pin on PCAP, which is the output of the A3 Amplifier. The HJACK\_DET line monitors the presence of a headset by using R453 (100k) as a pull-up resistor and detecting the voltage at A1\_INT of PCAP. A1\_INT is pulled down by Impedance of headset's left channel. If stereo headset is plugged, impedance is equal to impedance of headset's left channel speaker, in case of TTY or mono headset impedance is zero (direct connection to ground via headset plug).

The External Microphone input is connected to the accessory connector for the mobile phone. The path is routed through R454, C465 and L441 to the EXT\_MIC pin on PCAP. This signal feeds directly to the input multiplexer without an intervening gain stage.

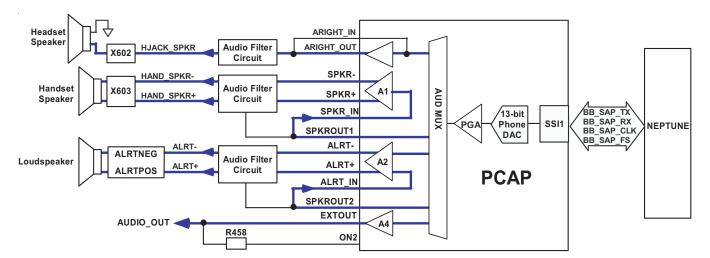

### PCAP RX Audio

The mobile phone supports four audio output paths. The output of PCAP's internal DAC drives the internal PGA. The output of the PGA can be routed to one of the four supported outputs via the internal multiplexer. These outputs connect to the SPKR+/- amplifier (Handset Earpiece Speaker), the ALERT+/- amplifier (Handset Loudspeaker/Alert Speaker), the EXTOUT amplifier (Accessory connector output), and the ARight Out amplifier (Headset Speaker). The single ended Alert mode amplifier (A2) is not used in this design. All outputs use the same D/A converter so only one output can be active at one time. The user can adjust the gain of the audio outputs with the volume control buttons.

The Handset Speaker is driven by PCAP's internal SPKR differential amplifier. Following the speaker path from the PCAP pins Speaker- and Speaker+, they are routed through L608 and L609 respectively, and then connected to the transducer via main flex, display flex and camera flex. Camera flex audio cir-

#### Figure 4-8 TX Audio Functional Block

#### PCAP RX Audio

cuitry includes 33pF shunt caps, coils, and 10pF shunt caps to remove audio buzz. Also 10ohm resistors are added to reduce signal level before ESD diode and transducer. Off the Speaker- path, SPKR\_IN is routed through C442 for the inverting input of the speaker amp A1. SPKR\_OUT1 from PCAP is routed through C440, R441 and C442 to Speaker-, which is the DAC output of the CODEC. SPKR\_IN and SPKR\_OUT1 will output their respective bias voltages on these pins during standby times. This is to maintain the voltage across an external coupling capacitor to avoid audio "pops" when the amplifier is enabled.

The headset uses a standard 2.5mm stereo phone jack (A630 SW supports only mono headset. HW supports stereo headset). The headset may contain a momentary switch, which is normally closed and is in series with the microphone cartridge. When the momentary switch is pressed, the bias current being supplied to the microphone will be interrupted. The phone will detect this action and make an appropriate response to this action, which could be to answer a call, end a call, or dial the last number from scratchpad.

A630

PCAP's internal Right amplifier drives the Headset Speaker. Following the speaker path from the PCAP pins ARight\_Out, the signal is routed through C489, R462 and L600, it is then connected to the headset jack. Off the ARight\_Out path, AR\_IN is tapped off through C482 for the inverting input of the audio amp ARIGHT.

The External Speaker is connected to pin 15 of X604 (AUDIO\_OUT ON/OFF), the accessory connector for the mobile phone. The audio path is routed from EXTOUT, of the PCAP, through R457, C469 and L606. The DC level of this Audio\_Out signal is also used to externally command the phone to toggle it's ON/OFF state. The Audio\_Out signal connects to PCAP's ON2 pin via R458 and V440 to provide this capability. When a DC level of <0.4V is applied by an accessory for a minimum of 700 milliseconds on the Audio\_Out line, the phone will toggle it's ON/ OFF state.

The Alert Transducer is driven by PCAP's ALRT amplifier (A2). The alert path from the PCAP pins ALRT- and ALRT+ are routed directly to the alert transducer. Off the ALRT- path, ALRT\_IN is routed

#### Figure 4-9 RX Audio Functional Block

through R460 and R461 for the inverting input of the alert amp A2. SPKROUT2 from PCAP is routed through C476 & C478 and R459 to ALRT-, which is the DAC output of the CODEC.

## **Battery Interface**

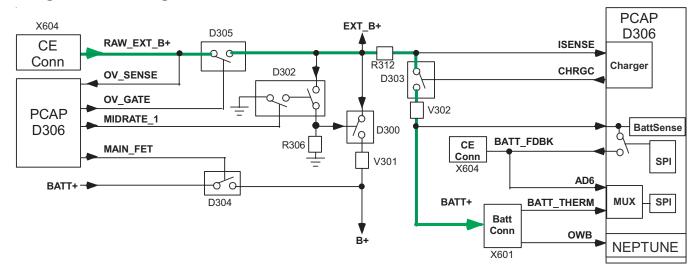

Batteries interface to the main transceiver board via a 4-pin connector (X601). Motorola approved removable Lithium Ion and Lithium Polymer batteries are supported. Upon power-up, the MCU (through its integrated One-Wire Interface Module) will interrogate the EPROM located inside the battery package to determine battery characteristics that impact radio and charging operations. Battery validity will also be verified. A thermistor element in the battery package provides temperature feedback.

During normal phone operation, without a charger attached, D304 is turned ON so that current can be supplied from the battery to the B+ power node on the transceiver board. When the phone is 'ON', the PCAP IC (D306) will enable its internal regulators so that transceiver circuitry can be enabled. When the phone is 'OFF', the PCAP IC disables its regulators to disable most active circuitry. In the OFF state, only minimal circuitry will be connected to B+ to minimize 'OFF' state leakage current.

Lithium Ion/Polymer charging is internally supported in the phone. Full rate charging is supported when a valid full rate charger is detected on the accessory interface (X604). During full rate charging, D300 is turned ON so that current can be supplied from the external source to B+. D304 will be turned OFF to disconnect the Battery from B+. Based on battery voltage and radio status, charging current will be set by controlling the voltage at the gate of D303. A sense resistor (R312) provides current sense feedback to the charger circuit. Battery charging will be disabled if an invalid battery is detected, if the radio is transmitting, if temperature is too high or too low, or if the battery voltage is too high.

Reduced rate charging is supported when a compatible lower capacity charger is detected on the accessory interface (X604). Operation with a reduced rate charger will not allow dead battery or 'no battery' operation.

#### Figure 4-10 Charger Functional Block

#### Neptune LTE

## **Neptune LTE**

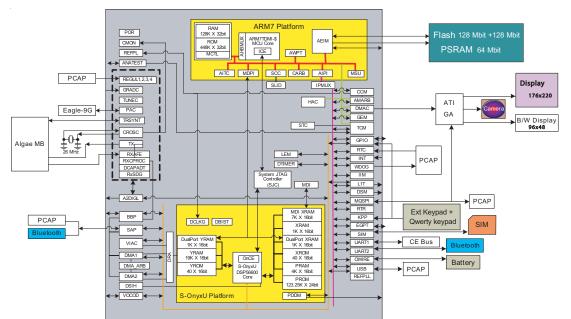

The Neptune LTE Baseband IC is a digital baseband processor for the 2.75G GSM Market. The design is derived from Neptune LTS with changes to memory configuration and several module enhancements. It is a dual-core processor that contains a Synthesizable Onyx DSP core (56600), an ARM7TDMI-S microcontroller, and custom peripherals.

The Neptune LTE IC is derived from the Neptune LT IC with the following key changes:

- Addition of Platform Independent Security Architecture (PISA) modules: — Security Controller (SCC),

- Memory Separation Unit (MSU)

- HASH Accelerator (HAC)

- On-chip memory:

- Changed MCU RAM size from 436Kbytes to 512Kbytes for GPRS production version, 256Kbytes for EDGE production version

- -Decreased MCU ROM size from

#### Figure 4-11 Neptune LTE Functional Block

3168Kbytes to 1792Kbytes

- Increased DSP X, Y, and P RAM and ROM sizes to support new features including EDGE

- Addition of OWIRE peripheral to support removable battery

- Addition of 2nd UART to support e.g. optional applications coprocessor

- Pin and GPIO muxing changes including — support for PCS's CE bus

- parallel DMAC

- dedicated BBP transmit pins for interface to external EDGE transmit IC

- DSP subsystem changes to support 130MHz required for EDGE

- Neptune LT MCU "PIG" peripheral bus has been omitted. All "PIG" peripherals are now accessed through the "IP" peripheral bus, and their base addresses have been changed (internal register organization remains the same).

## **Memory Interface**

The portable will be using a memory part containing 3 memory dies: two stacked 128Mbyte Burst Flash (STM M36LLR7760D0ZAQT) dies and a 64Mbyte PSRAM die. The portable products will be operating at 1.8V core voltages and will have a 1.8V interface to Neptune LTE.

Neptune LTS's AEIM will be interfaced to the stacked memory device and consists of the external address lines, data lines, chip selects, and memory control lines.

The two-memory die contained in the stacked CSP has a single chip select signal. CSP has an integrated chip select coding logic to access whole memory space with only one CS. Two internal CSs are created from the A24 and CS0 signals.

## **Keypad Interface**

#### General

The Keypad Port is a 16-bit peripheral, used generally for keypad matrix scanning, or as a GPIO port up to 16 bits wide. The keypad matrix can be configured up to 8 rows by 8 columns, with unused pins as GPIOs.

#### **3-Pole Solution**

A630 phone with 3-pole system is using enhanced keypad matrix with GPIO pins PC14 and USB\_SUSPEND mapped as extra columns. This is done to support 62-key keypad matrix.

For this phone, each row and column will be set as inputs; there is no need to strobe the columns. When a key is pressed, an interrupt will be generated and software will detect which pair of row(s) and/or column are low, then read the four bytes for each pair.

#### 2-Pole Solution

A630 phone with 2-pole system is using enhanced keypad matrix with GPIO pins PC14, USB\_SUSPEND, MISOB, SPI\_CS, TOUT12 and SPI\_CS8 mapped as extra columns, also URTSI is mapped to extra row. This is done to support 62-key keypad matrix with 2-pole system.

For this phone, each row will be set as input and each column will be set as output. When a key is pressed, an interrupt will be generated. Software will detect which row and column has been connected when key is pressed by strobe of the column lines.

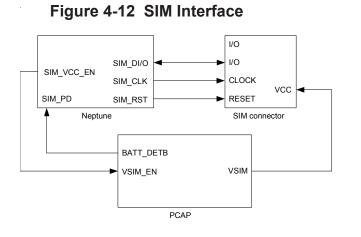

## **SIM Interface**

The SIM interface block is designed to facilitate communication to SIM cards or Eurochip pre-paid phone cards. The card itself stores important information including the subscriber telephone number, phone numbers, the users' PIN, and other information to be able to complete a phone call. The card holds all this information for the user and therefore must be protected from electro-static discharge that could destroy the card. We prevent this event by also requiring the user to attach a battery. Batteries on Motorola product are arranged in such a way to fully cover the SIM block.

The SIM block has two ports that can be used to interface with the various cards. The interface with the MCU is a 16-bit connection via the AIPI Controller and the IP-Bus Interface. Figure 4-12 shows the signals and direction of propagation between the different device modules.

PCAP can supply the SIM block with either 1.875 V or 3.0 V. The bit VSIM\_0 determines the voltage.

This is bit number 18 in the AUX\_VREG register (location 07). The 5 V SIM cards are not supported with this architecture. A630 SW supports only 3V SIM.

The VSIM regulators on and off state will be controlled by one SPI bit (VSIM\_EN) and one external pin (SIM\_VCCEN). SIM\_VCCEN is a pin on Neptune that connects to the VSIM\_EN pin of PCAP. The SIM regulator will be on only when the SIM\_VCCEN pin and the VSIM\_EN SPI bit are logic high. The voltage supply to the card must be shut down before the SIM card is removed and the card loses contact with the radio. Because of the nature of the removable SIM card the SIM regulator must be able to withstand a short circuit at its output without sustaining any damage.

The SIM module contains a block designed specifically for generating the clocks used internal to the SIM module, and the clocks provided to the SIM cards.

There are no interrupt sources generated by the SIM clock generator block.

The SIM Transmitter block contains the transmit state machine, transmit shift register, and transmit FIFO.

The SIM Receiver block contains the receive state machine, receive FIFO, and control logic.

On power up, the phone checks for connected accessories and for the validity of battery voltage. If the battery voltage is valid then the SIM Card is secure and the phone attempts to read data from the SIM on the SIM\_I/O line. If no data is read then that indicates that a card is not present and S/W should write "CHECK CARD" to the display.

The SIMPD input allows for detection of the insertion or removal of a SIM card. A maskable interrupt can be generated when a SIMPD event occurs. An internal 69k pullup is present on the SIMPD pin for Neptune. This will provide for a high to low transition on the SIMPD pin when a SIM card is removed.

The SIM port control block contains hardware that provides the correct sequence to power down a SIM card. The software must perform the power-up sequence.

The power down sequence is:

RST transitions from high to low CLK is turned off to a low I/O transitions from tri-state to low SIM Vcc is turned off

The SIM module is capable of forcing a SIM card power down. It is similar to the auto power down feature, except that it is not dependent upon either the state of the SIM card auto power down enable bit, or triggering of a presence detect event.

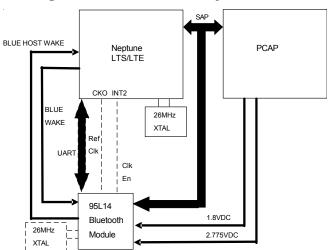

## Bluetooth

The HCI interface will utilize an UART. There are two data signals (TXD and RXD) and two flow control signals (RTS and CTS). The BT module assumes a role as DTE and the Neptune LTS/LTE acts as a DCE. Therefore when the BT module is connected to Neptune LTS/LTE the RXD and TXD lines must be crossed, while CTS and RTS on Neptune connect directly to CTS and RTS on the BT module. RXD and TXD have been crossed on the BT module already; therefore, BLUE\_TX (pin 5) of the BT module is connected to TXD2 (pin N13) and BLUE\_RX (pin 33) of the BT module is connected to RXD2 (pin N17) on Neptune LTS/LTE 257 pin package.

The Bluetooth UART is a dedicated UART from Neptune LTS/LTE. This bus is not shared with external peripherals.

Although most signaling is done over the HCI, wakeup signaling is done with dedicated signals. Neptune LTS/LTE uses a GPIO (PC12/pin D14) to wake up the BT module. The BT module uses a dedicated signal BLUE\_HOST\_WAKEB (Pin 9) connected to a Neptune LTS/LTE interrupt (INT 5) to wake-up the host processor.

Figure 4-13 Bluetooth System Block

The codec is connected onto a shared 4 wire bus with Neptune LTS/LTE and PCAP referred to as the

BB\_SAP (Base Band Serial Audio Codec Port). The PCAP acts as the master and provides the clock and frame sync signals for the bus. The labeling on the Bluetooth module is in reference to the Neptune LTS/ LTE. Therefore, the ASAP\_TX line is an input and ASAP\_RX is the output from Bluetooth.

Bluetooth is reset in a number of different ways. When software first initializes Bluetooth, it sends an HCI reset command over the UART interface to place the BCM2035 into a known state.

If software fails to detect a response to the initial HCI reset command, it will power cycle the RF and Core voltages thus forcing a power on reset on the BCM2035.

Bluetooth is reset in start-up using the RESETB signal; it is connected to RESET\_N (pin 22) of the BT module. RESET\_N is active low.

The Broadcom chipset requires two different frequency references, a lower frequency low power reference (32.768 kHz), and a high frequency main reference (15.36 MHz, 26 MHz, etc.). The low power reference is a standard frequency available on the GSM phone whenever the phone is powered. As such, this reference is directly connected to CLK\_32KHZ, the buffered port from the oscillator on PCAP.

As this module will be primarily used on GSM platform, PLL components on the module were tuned for 26 MHz with the intent to share the crystal frequency oscillator of the phone, Neptune LTS XTAL OSC.

Unlike the low power reference, the Neptune XTAL OSC, is not available all the time and does not provide a dedicated buffered output. When Bluetooth requires this reference when being paged, it must wake up its host processor (Neptune LTS) if it is in deep sleep. When the Bluetooth switches to the main reference it should not disturb the Neptune LTS XTAL

#### Flip Interface

OSC circuit in regards to frequency, or noise performance, thereby dictating some amount of isolation or buffering.

This option would use a 2.5 x 3.2 mm discrete 26 MHz crystal with two shunt capacitors (15 pF). The XTAL circuit oscillator is contained on the BCM2035 and enables itself without any control from the host processor.

The host processor, though, must program a trim value to the Bluetooth module via an HCI command every time the Bluetooth module is POR. This trim value is programmed in the phone's SEEM at the time of factory phasing.

CKO is a multiplexed clock output available from Neptune LTS.

Software will need to program Neptune LTS/LTE to configure the CKO pin to use this uncorrected clock on every POR. Enabling signal for this option will be via the BLUE\_CLK\_ENB signal which is connected to interrupt INT2 of Neptune LTS/LTE.

Software will also need to provide a trim value to the Bluetooth module on every POR as with the case for the discrete Oscillator Buffer described above.

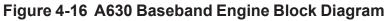

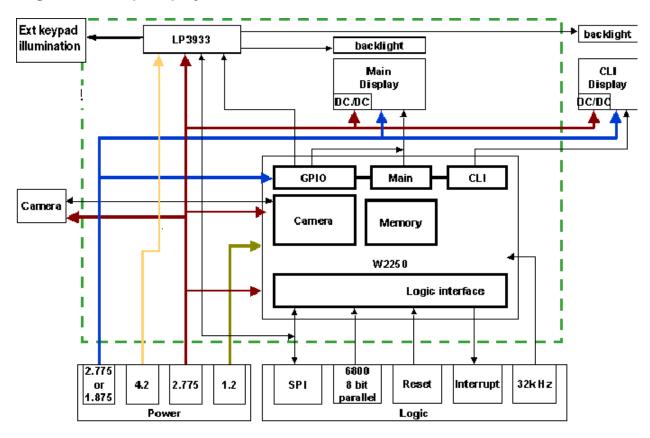

## **Flip Interface**

The Flip Display Module functions as a core display subassembly that also supports an external Caller ID (CLI) display in 96x48 inversed B/W LCD formats.

The module's interface is a 40 pin board-to-board connector designed to accept a product-specific FPC. This FPC (Main Flex) has a connector interface to the phone, along with interfaces to various phone components such as receiver, vibrator, external keypad and external keypad illumination. The external keypad interface on Main Flex is a 20 pin board-toboard connector. This connector interface includes signals of keypad matrix and keypad illumination LEDs.

Keypad flex is connected to 20 pin board-to-board connector of Main Flex. This FPC includes keypad matrix of external keypad and keypad's LED back-light.

The Caller ID interface is a 13 pin ZIF connector designed to mate with a 96x48 B/W CLI module.

The Camera interface is a 24 pin ZIF connector designed to mate with the CMOS camera module. 20 pins of 24 are used for camera interface; rest 4 pins are used for receiver differential audio signals HAND\_SPKR+ and HAND\_SPKR+ and two audio grounds.

Figure 4-14 Flip Display Module

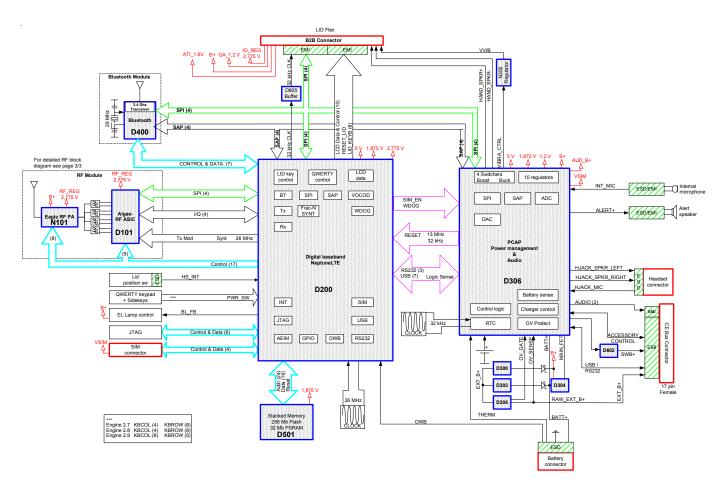

## **Block Diagrams**

Block diagrams of the A630 are illustrated below.

| nal Name | EXC_EN    | LOWB_HIGH | EUROB_US | Radio Mode |                   |

|----------|-----------|-----------|----------|------------|-------------------|

| in       | TX_ANT_EN | LOWB HIGH | EUROB_US |            |                   |

|          | 0         | 0         | 0        | RX EGSM    | Low Current State |

|          | 0         | 0         | 1        | RX CEL     |                   |

|          | 0         | 1         | 0        | RX DCS     | Low Current State |

|          | 0         | 1         | 1        | RX PCS     |                   |

|          | 1         | 0         | 0        | TX EGSM    |                   |

|          | 1         | 0         | 1        | TX CEL     |                   |

|          | 1         | 1         | 0        | TX DCS     |                   |

|          | 1         | 1         | 1        | TX PCS     |                   |