# MSM6550/MSM6150™ Mobile Station Modem

Software Interface

80-V7196-2 Rev. A June 24, 2004

**QUALCOMM®** Proprietary

**Restricted Distribution.** This document contains critical information about QUALCOMM products and may not be distributed to anyone that is not an employee of QUALCOMM without the approval of Configuration Management.

5775 Morehouse Drive San Diego, CA 92121-1714 U.S.A. QUALCOMM Incorporated 5775 Morehouse Drive San Diego, CA 92121-1714 U.S.A.

Copyright © 2004 QUALCOMM Incorporated. All rights reserved.

All data and information contained in or disclosed by this document are confidential and proprietary information of QUALCOMM Incorporated, and all rights therein are expressly reserved. By accepting this material, the recipient agrees that this material and the information contained therein are held in confidence and in trust and will not be used, copied, reproduced in whole or in part, nor its contents revealed in any manner to others without the express written permission of QUALCOMM Incorporated.

Export of this technology may be controlled by the United States Government. Diversion contrary to U.S. law prohibited.

**Restricted Distribution.** This document contains critical information about QUALCOMM products and may not be distributed to anyone that is not an employee of QUALCOMM without the approval of Configuration Management.

QUALCOMM is a registered trademark and registered service mark of QUALCOMM Incorporated. Other product and brand names may be trademarks or registered trademarks of their respective owners.

Information in this document is preliminary and subject to change and does not represent a commitment on the part of QUALCOMM Incorporated.

Send technical questions to: https://support.cdmatech.com

MSM6550 / MSM6150 $^{TM}$  Software Interface 80-V7196-2 Rev. A

# Contents

|   | Cont  | tent                   |                     | iii    |

|---|-------|------------------------|---------------------|--------|

|   | Figu  | res                    |                     | xxxv   |

|   | Table | es                     |                     | xxxvii |

| 1 | Intro | duction                |                     |        |

|   | 1.1   | Overview               |                     | 1-1    |

|   | 1.2   | Definitions/guidelines |                     | 1-2    |

|   | 1.3   | Register categories    |                     | 1-3    |

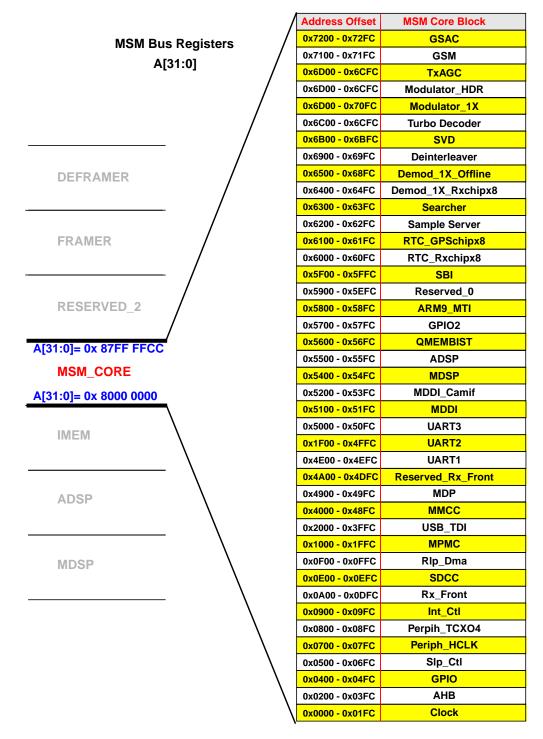

|   | 1.4   | ARM address map sur    | mmary               | 1-4    |

|   |       | 1.4.1 MSM_C0           | ORE region          | 1-5    |

|   | 1.5   |                        |                     |        |

| 2 | Cloc  | ks                     |                     |        |

|   | 2.1   | ARM registers          |                     | 2-1    |

|   |       | 0x0000                 | MSM_CLK_HALTA       | 2-1    |

|   |       | 0x0004                 | MSM_CLK_HALTB       | 2-4    |

|   |       | 0x0008                 | Reserved.           | 2-5    |

|   |       | 0x000C                 | Reserved.           | 2-5    |

|   |       | 0x0010                 | DSP_DMA_CLK_OVR_REG | 2-5    |

|   |       | 0x0014                 | MISC_CLK_CTL        | 2-6    |

|   |       | 0x0018                 | MSM_CLK_RINGOSC     | 2-9    |

|   |       | 0x001C                 | TCXO_CNT            | 2-10   |

|   |       | 0x0020                 | RINGOSC_CNT         | 2-10   |

|   |       | 0x0024                 | MSM_CLK_SLEEPOSC    | 2-10   |

|   |       | 0x0028                 | MSM_CLK_USBOSC      | 2-11   |

|   |       | 0x0030                 | PLL0_MODE           | 2-12   |

|   |       | 0x0034                 | PLL0_L_VAL          | 2-13   |

|   |       | 0x0038                 | PLL0_M_VAL          | 2-13   |

|   |       | 0x003C                 | PLL0_N_VAL          | 2-13   |

| 0x004C | PLL1_MODE        | 2-14 |

|--------|------------------|------|

| 0x0050 | PLL1_L_VAL       | 2-15 |

| 0x0054 | PLL1_M_VAL       | 2-15 |

| 0x0058 | PLL1_N_VAL       | 2-15 |

| 0x0068 | DCPLL0_MODE      | 2-16 |

| 0x006C | DCPLL0_LVAL      | 2-16 |

| 0x007C | DCPLL1_MODE      | 2-16 |

| 0x0080 | DCPLL1_LVAL      | 2-17 |

| 0x0090 | CHIPXN_CLK_MD    | 2-17 |

| 0x0094 | CHIPXN_CLK_NS    | 2-18 |

| 0x0098 | GPSCHIPXN_CLK_MD | 2-19 |

| 0x009C | GPSCHIPXN_CLK_NS | 2-19 |

| 0x00A0 | ADSP_CLK_MD      | 2-20 |

| 0x00A4 | ADSP_CLK_NS      | 2-21 |

| 0x00A8 | MDSP_CLK_MD      | 2-22 |

| 0x00AC | MDSP_CLK_NS      | 2-22 |

| 0x00B8 | OFFLINE_CLK_MD   | 2-23 |

| 0x00BC | OFFLINE_CLK_NS   | 2-24 |

| 0x00C8 | ICODEC_CLK_MD    | 2-25 |

| 0x00CC | ICODEC_CLK_NS    | 2-25 |

| 0x00D0 | ECODEC_CLK_MD    | 2-26 |

| 0x00D4 | ECODEC_CLK_NS    | 2-27 |

| 0x00D8 | SDAC_CLK_MD      | 2-28 |

| 0x00DC | SDAC_CLK_NS      | 2-28 |

| 0x00E0 | GSM_CLK_MD       | 2-29 |

| 0x00E4 | GSM_CLK_NS       | 2-30 |

| 0x00E8 | GP_CLK_MD        | 2-31 |

| 0x00EC | GP_CLK_NS        | 2-31 |

| 0x00F0 | CAMCLK_PO_CLK_MD | 2-32 |

| 0x00F4 | CAMCLK_PO_CLK_NS | 2-32 |

| 0x00F8 | SDCC_MCLK_MD     | 2-34 |

| 0x00FC | SDCC_MCLK_NS     | 2-34 |

| 0x0100 | MDDI_HOST_CLK_MD | 2-35 |

| 0x0104 | MDDI_HOST_CLK_NS | 2-35 |

| 0x0108 | MICRO_CLK_MD     | 2-36 |

| 0x010C | MICRO_CLK_NS     | 2-37 |

| 0x0110 | MICRO_ACTIVE_MD  | 2-38 |

| 0x0114 | MICRO_ACTIVE_NS  | 2-38 |

| 0x0118 | CHAIN0_CLK_SEL   | 2-38 |

| 0x011C | CHAIN1_CLK_SEL   | 2-39 |

|   |     |        | 0x0120           | MISC_CLK_SEL1            | 2-40 |

|---|-----|--------|------------------|--------------------------|------|

|   |     |        | 0x0124           | MISC_CLK_SEL2            | 2-42 |

|   |     |        | 0x0128           | ANALOG_CLK0_SEL          | 2-43 |

|   |     |        | 0x012C           | ANALOG_CLK1_SEL          | 2-44 |

|   |     |        | 0x0130           | MSM_CLK_INV1             | 2-45 |

|   |     |        | 0x0134           | MSM_CLK_INV2             | 2-46 |

|   |     |        | 0x0138           | GLOBAL_RESET             | 2-47 |

|   |     |        | 0x013C           | MSM_CLK_FS_ON            | 2-48 |

|   |     |        | 0x0140           | MSM_CLK_FS_CNT           | 2-49 |

|   |     |        | 0x0144           | GPS_SETUP                | 2-50 |

|   |     |        | 0x0148           | SWITCH_REF_CLK_SEL       | 2-50 |

|   |     |        | 0x014C           | ARM_MEMORY_EDGE_EN       | 2-51 |

| 3 | AHB |        |                  |                          |      |

|   | 3.1 | ARM AH | IB_REGS register | rs                       | 3-1  |

|   |     | 3.1.1  | ARM clock co     | ontroller registers      | 3-1  |

|   |     |        | 0x0000           | SWITCH_CLK               | 3-1  |

|   |     |        | 0x0004           | MICRO_CLK_OFF            | 3-2  |

|   |     |        | 0x000C           | HCLK_DIV                 | 3-2  |

|   |     | 3.1.2  | AHB reset/pau    | ise controller registers | 3-2  |

|   |     |        | 0x0020           | PAUSE_TIMER              | 3-2  |

|   |     |        | 0x0024           | RESET_STATUS             | 3-3  |

|   |     | 3.1.3  | Interface confi  | guration register        | 3-3  |

|   |     |        | 0x0040           | MDSP_INTF_CFG            | 3-3  |

|   |     |        | 0x0044           | ADSP_INTF_CFG            | 3-4  |

|   |     |        | 0x0048           | IMEM_CFG                 | 3-4  |

|   |     |        | 0x004C           | MSM_BRIDGE_CFG           | 3-5  |

|   |     | 3.1.4  | EBI1 registers   |                          | 3-6  |

|   |     |        | 0x0060           | EBI1_CFG                 | 3-6  |

|   |     |        | 0x0064           | EBI1_MPMC_STDY_SEL       | 3-10 |

|   |     |        | 0x0068           | EBI1_PSRAM_CRE           | 3-11 |

|   |     |        | 0x006C+0x8n      | EBI1_CSn_CFG0, n=[0,3]   | 3-11 |

|   |     |        | 0x0070+0x8n      | EBI1_CSn_CFG1, n=[0,3]   | 3-14 |

|   |     |        | 0x008C           | EBI1_MEM_CTLR_SEL_CMD    | 3-17 |

|   |     |        | 0x0090           | EBI1_MEM_CTLR_SEL_STATUS | 3-17 |

|   |     | 3.1.5  | EBI2 registers   |                          | 3-18 |

|   |     |        | 0x00B0           | EBI2_CFG                 | 3-18 |

|   |     |        | 0x00B4           | LCD_CFG0                 | 3-19 |

|   |     |        | 0x00B8           | LCD_CFG1                 | 3-20 |

|   |     |        | 0x00BC+0x8n      | GPn_CFG0, n=[0.3]        | 3-21 |

|     |         | 0x00C0+0x8n      | GPn_CFG1, n=[0,3]   | 3-23 |

|-----|---------|------------------|---------------------|------|

|     |         | 0x00DC           | ETM_GPIO2_CFG       | 3-24 |

|     | 3.1.6   | Boot ECC stat    | us registers        | 3-24 |

|     |         | 0x100            | BOOT_ECC_SELF_ERR   | 3-24 |

|     |         | 0x0104           | BOOT_ECC_CORRECTED  | 3-25 |

|     | 3.1.7   | BOOT control     | registers           | 3-26 |

|     |         | 0x0120           | BOOT_MODE_STATUS    |      |

|     | 3.1.8   | Delay control    | register            | 3-26 |

|     |         | 0x0130           | DELAY_CNTL          | 3-26 |

| 3.2 | ARM Fra | mer registers    |                     | 3-27 |

|     |         | 0x0000           | FRAMER_CMD          | 3-27 |

|     |         | 0x0004           | FRAMER_ACCM_VALUE   | 3-27 |

|     |         | 0x0008           | FRAMER_BYTE_CNT     | 3-27 |

|     |         | 0x0018           | FRAMER_CTL          | 3-28 |

|     |         | 0x0080           | FRAMER_DATA_IN      | 3-28 |

|     |         | 0x00C0           | FRAMER_DATA_OUT     |      |

| 3.3 | ARM De  | framer registers |                     | 3-29 |

|     |         | 0x0000           | DEFRAMER_CMD        | 3-29 |

|     |         | 0x0004           | DEFRAMER_HEADER_CNT | 3-29 |

|     |         | 0x0008           | DEFRAMER_BYTE_CNT   | 3-29 |

|     |         | 0x000C           | Reserved            | 3-29 |

|     |         | 0x0080           | DEFRAMER_DATA_IN    | 3-30 |

|     |         | 0x00C0           | DEFRAMER_DATA_OUT   | 3-30 |

| MPN | IC      |                  |                     |      |

| 4.1 |         | isters           |                     | 4-1  |

|     |         | 0x000            | MPMC CONTROL        |      |

|     |         | 0x004            | MPMC_STATUS         |      |

|     |         | 0x008            | MPMC_CONFIG         |      |

|     |         | 0x020            | MPMC_DY_CNTL        | 4-2  |

|     |         | 0x024            | MPMC_DY_REF         | 4-3  |

|     |         | 0x028            | MPMC_DY_TRD_CFG     | 4-3  |

|     |         | 0x030            | MPMC_DY_TRP         | 4-3  |

|     |         | 0x034            | MPMC_DY_TRAS        | 4-4  |

|     |         | 0x038            | MPMC_DY_TSREX       | 4-4  |

|     |         | 0x03C            | MPMC_DY_TAPR        | 4-4  |

|     |         | 0x040            | MPMC_DY_TDAL        | 4-5  |

|     |         | 0x044            | MPMC_DY_TWR         | 4-5  |

|     |         | 0x048            | MPMC_DY_TRC         | 4-5  |

|     |         | 0x04C            | MPMC_DY_TRFC        | 4-6  |

vii

| 0x050 | MPMC_DY_TXSR4-       | -6 |

|-------|----------------------|----|

| 0x054 | MPMC_DY_TRRD4        | -6 |

| 0x058 | MPMC_DY_TMRD4        | -7 |

| 0x080 | MPMC_ST_EXD_WT4      | -7 |

| 0x100 | MPMC_DY_CONFIG04     | -7 |

| 0x104 | MPMC_DY_RAS_CAS04    | -8 |

| 0x120 | MPMC_DY_CONFIG14     | -8 |

| 0x124 | MPMC_DY_RAS_CAS14    | -8 |

| 0x140 | MPMC_DY_CONFIG24     | .9 |

| 0x144 | MPMC_DY_RAS_CAS24    | .9 |

| 0x160 | MPMC_DY_CONFIG34     | .9 |

| 0x164 | MPMC_DY_RAS_CAS34-1  | .0 |

| 0x200 | MPMC_ST_CONFIG04-1   | 0  |

| 0x204 | MPMC_ST_W_TWEN04-1   | .0 |

| 0x208 | MPMC_ST_W_TOEN04-1   | .1 |

| 0x20C | MPMC_ST_W_TRD04-1    | .1 |

| 0x210 | MPMC_ST_W_TPG04-1    | .1 |

| 0x214 | MPMC_ST_W_TWR04-1    | .2 |

| 0x218 | MPMC_ST_W_TTURN04-1  | .2 |

| 0x220 | MPMC_ST_CONFIG14-1   | 2  |

| 0x224 | MPMC_ST_W_TWEN14-1   | .3 |

| 0x228 | MPMC_ST_W_TOEN14-1   | .3 |

| 0x22C | MPMC_ST_W_TRD14-1    | .3 |

| 0x230 | MPMC_ST_W_TPG14-1    | .4 |

| 0x234 | MPMC_ST_W_TWR14-1    | 4  |

| 0x238 | MPMC_ST_W_TTURN14-1  | .4 |

| 0x240 | MPMC_ST_CONFIG24-1   | .5 |

| 0x244 | MPMC_ST_W_TWEN24-1   | .5 |

| 0x248 | MPMC_ST_W_TOEN24-1   | .5 |

| 0x24C | MPMC_ST_W_TRD24-1    | 6  |

| 0x250 | MPMC_ST_W_TPG24-1    | 6  |

| 0x254 | MPMC_ST_W_TWR24-1    | 6  |

| 0x258 | MPMC_ST_W_TTURN24-1  | .7 |

| 0x260 | MPMC_ST_CONFIG34-1   | .7 |

| 0x264 | MPMC_ST_W_TWEN34-1   | .7 |

| 0x268 | MPMC_ST_W_TOEN34-1   | 8  |

| 0x26C | MPMC_ST_W_TRD34-1    | 8  |

| 0x270 | MPMC_ST_W_TPG34-1    | .8 |

| 0x274 | MPMC_ST_W_TWR34-1    | 9  |

| 0x278 | MPMC ST W TTURN3 4-1 | 9  |

|   |        |           | 0xF00       | MPMCITCR                       | 4-19 |

|---|--------|-----------|-------------|--------------------------------|------|

|   |        |           | 0xF20       | MPMCITIP                       | 4-20 |

|   |        |           | 0xF40       | MPMCITOP                       | 4-20 |

|   |        |           | 0xFD0       | MPMC_PERIPH_ID4                | 4-20 |

|   |        |           | 0xFD4       | MPMC_PERIPH_ID5                | 4-21 |

|   |        |           | 0xFD8       | MPMC_PERIPH_ID6                | 4-21 |

|   |        |           | 0xFDC       | MPMC_PERIPH_ID7                | 4-21 |

|   |        |           | 0xFE0       | MPMC_PERIPH_ID0                | 4-22 |

|   |        |           | 0xFE4       | MPMC_PERIPH_ID1                | 4-22 |

|   |        |           | 0xFE8       | MPMC_PERIPH_ID2                | 4-22 |

|   |        |           | 0xFEC       | MPMC_PERIPH_ID3                | 4-23 |

|   |        |           | 0xFF0       | MPMC_PCELL_ID0                 | 4-23 |

|   |        |           | 0xFF4       | MPMC_PCELL_ID1                 | 4-23 |

|   |        |           | 0xFF8       | MPMC_PCELL_ID2                 | 4-24 |

|   |        |           | 0xFFC       | MPMC_PCELL_ID3                 | 4-24 |

| 5 | NAN    | D Flash N | Memory Inte | erface                         |      |

|   | 5.1    |           |             |                                | 5-1  |

|   | 5.2    |           |             |                                |      |

|   |        |           | 0x0300      | NAND_FLASH_CMD                 |      |

|   |        |           | 0x0304      | NAND_FLASH_ADDR                |      |

|   |        |           | 0x0308      | NAND_FLASH_STATUS              |      |

|   |        |           | 0x030C      | NAND_FLASH_ECC_0               |      |

|   |        |           | 0x0310      | NAND_FLASH_ECC_1               |      |

|   |        |           | 0x0314      | NAND_FLASH_ECC_2               |      |

|   |        |           | 0x0318      | NAND_FLASH_ECC_3               |      |

|   |        |           | 0x031C      | NAND_FLASH_CFG1                |      |

|   |        |           | 0x0320      | NAND_FLASH_CFG2                |      |

|   |        |           | 0x0324      | NAND_SPARE_DATA                |      |

| _ | la tau |           | (II         |                                |      |

| 6 |        | rupt Con  |             |                                | 6.1  |

|   | 6.1    | _         |             |                                |      |

|   |        | 6.1.1     | •           | ontroller write registers      |      |

|   |        |           | 0x0000      | INT_CLEAR_0                    |      |

|   |        |           | 0x0004      | INT_CLEAR_1                    |      |

|   |        |           | 0x0008      | GPIO_INT_CLEAR_0               |      |

|   |        |           | 0x000C      | GPIO_INT_CLEAR_1               |      |

|   |        |           | 0x0010      | GPIO_INT_CLEAR_4               |      |

|   |        | 6.1.2     | *           | ontroller read/write registers |      |

|   |        |           | 0x0014      | IRQ_EN_0                       |      |

|   |        |           | 0x0018      | IRO EN 1                       | 6-7  |

|            |             | 0x001C       | FIQ_EN_0                        | 6-8  |

|------------|-------------|--------------|---------------------------------|------|

|            |             | 0x0020       | FIQ_EN_1                        | 6-10 |

|            |             | 0x0024       | GPIO_INT_EN_0                   | 6-11 |

|            |             | 0x0028       | GPIO_INT_EN_1                   | 6-11 |

|            |             | 0x002C       | GPIO_INT_EN_4                   | 6-12 |

|            |             | 0x0030       | INT_POLARITY_0                  | 6-12 |

|            |             | 0x0034       | INT_POLARITY_1                  | 6-12 |

|            |             | 0x0038       | INT_POLARITY_2                  | 6-13 |

|            |             | 0x003C       | INT_POLARITY_5                  | 6-13 |

|            |             | 0x0048       | GPIO_INT_DETECT_CTL_0           | 6-13 |

|            |             | 0x004C       | GPIO_INT_DETECT_CTL_1           | 6-14 |

|            |             | 0x0050       | GPIO_INT_DETECT_CTL_4           | 6-14 |

|            | 6.1.3       | Interrupt co | ontroller read registers        | 6-15 |

|            |             | 0x0054       | INT_STATUS_0                    | 6-15 |

|            |             | 0x0058       | INT_STATUS_1                    | 6-16 |

|            |             | 0x005C       | GPIO_INT_STATUS_0               | 6-18 |

|            |             | 0x0060       | GPIO_INT_STATUS_1               | 6-18 |

|            |             | 0x0064       | GPIO_INT_STATUS_4               | 6-18 |

| 2one       | aral Burn   | ose I/O (GP  | 10)                             |      |

| 7.1        | -           | •            | •                               | 7.1  |

| 7.1<br>7.2 |             |              |                                 |      |

| 1.2        | _           |              |                                 |      |

|            | 7.2.1       | _            | ut value registers              |      |

|            |             | 0x0000       | GPIO_OUT_0                      |      |

|            |             | 0x0004       | GPIO_OUT_1                      |      |

|            |             | 0x0008       | GPIO_OUT_4                      |      |

|            | <b>5.00</b> | 0x000C       | GPIO_OUT_5                      |      |

|            | 7.2.2       | •            | ut enabling registers           |      |

|            |             | 0x0010       | GPIO_OE_0                       |      |

|            |             | 0x0014       | GPIO_OE_1                       |      |

|            |             | 0x0018       | GPIO_OE_4                       |      |

|            |             | 0x001C       | GPIO_OE_5                       |      |

|            | 7.2.3       | •            | ut alternate-function registers |      |

|            |             | 0x0020       | GPIO_PAGE                       |      |

|            |             | 0x0024       | GPIO_CFG                        |      |

|            | 7.2.4       | •            | t value registers               |      |

|            |             | 0x0034       | GPIO_IN_0                       |      |

|            |             | 0x0038       | GPIO_IN_1                       | 7-19 |

|            |             | 0x003C       | GPIO_IN_4                       | 7-19 |

|            |             | 0x0040       | GPIO IN 5                       | 7-19 |

| Ö  | GPIU               | 2        |              |                       |      |

|----|--------------------|----------|--------------|-----------------------|------|

|    | 8.1                | ARM reg  | isters       |                       | 8-1  |

|    |                    |          | 0x0000       | GPIO_OE_2             | 8-1  |

|    |                    |          | 0x0004       | GPIO_OE_3             | 8-2  |

|    |                    |          | 0x0008       | GPIO_OUT_2            | 8-2  |

|    |                    |          | 0x000C       | GPIO_OUT_3            | 8-2  |

|    |                    |          | 0x0010       | GPIO_INT_DETECT_CTL_2 | 8-2  |

|    |                    |          | 0x0014       | GPIO_INT_DETECT_CTL_3 | 8-3  |

|    |                    |          | 0x0018       | INT_POLARITY_3        | 8-3  |

|    |                    |          | 0x001C       | INT_POLARITY_4        | 8-3  |

|    |                    |          | 0x0020       | GPIO_INT_EN_2         | 8-3  |

|    |                    |          | 0x0024       | GPIO_INT_EN_3         | 8-4  |

|    |                    |          | 0x0028       | GPIO_INT_CLEAR_2      | 8-4  |

|    |                    |          | 0x002C       | GPIO_INT_CLEAR_3      | 8-4  |

|    |                    |          | 0x0030       | GPIO2_PAGE            | 8-5  |

|    |                    |          | 0x0034       | GPIO2_CFG             | 8-5  |

|    |                    |          | 0x0040       | GPIO_IN_2             | 8-9  |

|    |                    |          | 0x0044       | GPIO_IN_3             | 8-9  |

|    |                    |          | 0x0048       | GPIO_INT_STATUS_2     | 8-9  |

|    |                    |          | 0x004C       | GPIO_INT_STATUS_3     | 8-9  |

|    |                    |          | 0x0050       | KEYSENSE_RD           | 8-10 |

| 9  | Anal               | og SBI   |              |                       |      |

|    | 9.1                | Analog S | BI registers |                       | 9-1  |

| 10 | Real               | Time Co  | unter        |                       |      |

|    | 10.1 ARM registers |          |              |                       | 10-1 |

|    |                    | 10.1.1   |              | HPX8 clock registers  |      |

|    |                    | 101111   | 0x0000       | CDMA_RTC_SYNC         |      |

|    |                    |          | 0x0004       | RTC CNT 1X            |      |

|    |                    |          | 0x0008       | RTC_SLEEP             |      |

|    |                    |          | 0x000C       | RTC_OFFSET            |      |

|    |                    |          | 0x0010       | RTC LOAD              |      |

|    |                    |          | 0x0014       | RTC CTL               |      |

|    |                    |          | 0x0018       | RTC_GP_COMPARE1       |      |

|    |                    |          | 0x001C       | RTC_GP_COMPARE2       |      |

|    |                    |          | 0x0020       | RTC_DIFF_1XHDR        |      |

|    |                    | 10.1.2   |              | X8 clock registers    |      |

|    |                    | 10.1.2   | 0x0000       | GPS_RTC_CTL           |      |

|    |                    |          | 0x0004       | GPS RTC CNT           |      |

|    |                    |          |              |                       |      |

#### 11 Receive Front-End

| 11.1 | ARM regi | sters                                  |                               |

|------|----------|----------------------------------------|-------------------------------|

|      | 11.1.1   | Rx Front regist                        | ters                          |

|      |          | 0x0+0x200c                             | RXFc_RESET, c=[0,1]11-2       |

|      |          | 0x4+0x200c                             | Reserved. 11-2                |

|      |          | 0x8+0x200c                             | Reserved. 11-2                |

|      |          | 0xC+0x200c                             | Reserved. 11-2                |

|      |          | 0x10+0x200c                            | Reserved. 11-2                |

|      |          | 0x14+0x200c                            | Reserved. 11-2                |

|      |          | 0x18+0x200c                            | RXFc_DVGA_CTL, c=[0,1]11-2    |

|      |          | 0x1C+0x200c                            | Reserved. 11-3                |

|      |          | 0x20+0x200c                            | Reserved. 11-3                |

|      |          | 0x24+0x200c                            | Reserved. 11-3                |

|      |          | 0x28+0x200c                            | Reserved. 11-3                |

|      |          | 0x2C+0x200c                            | Reserved. 11-3                |

|      |          | 0x30+0x200c                            | Reserved. 11-3                |

|      |          | 0x34+0x200c                            | Reserved. 11-3                |

|      |          | 0x38+0x200c                            | Reserved. 11-3                |

|      |          | 0x3C+0x200c                            | Reserved. 11-3                |

|      |          | 0x40+0x200c                            | Reserved. 11-3                |

|      |          | 0x44+0x200c                            | Reserved. 11-3                |

|      |          | 0x48+0x200c                            | Reserved. 11-3                |

|      |          | 0x4C+0x200c                            | Reserved. 11-3                |

|      |          | 0x50+0x200c                            | Reserved. 11-3                |

|      |          | 0x64+0x200c                            | Reserved. 11-3                |

|      |          | 0x78+0x200c                            | Reserved. 11-3                |

|      |          | 0x7C+0x200c                            | Reserved. 11-3                |

|      |          | 0x80+0x200c                            | Reserved. 11-3                |

|      |          | 0x84+0x200c                            | Reserved. 11-4                |

|      |          | 0x88+0x200c                            | Reserved. 11-4                |

|      |          | 0x8C+0x200c                            | Reserved. 11-4                |

|      |          | 0x90+0x200c                            | Reserved. 11-4                |

|      |          | 0x98+0x200c                            | Reserved. 11-4                |

|      |          | 0xAC+0x200c                            | Reserved. 11-4                |

|      |          | 0xB0+0x200c                            | Reserved. 11-4                |

|      |          | 0xB4+0x200c                            | Reserved. 11-4                |

|      | 11.1.2   | Rx AGC Regis                           | ters11-5                      |

|      |          | 0xC0+0x200c                            | RX_AGCc_RESET, c=[0,1]11-5    |

|      |          | 0xC4+0x200c                            | RX_AGCc_MODE_SEL, c=[0,1]11-5 |

|      |          | $0 \times C \times 0 \times 200 \circ$ | DV AGC   CLUT LVAL c=[0.1]    |

**12**

|       |        | 0xCC+0x200c     | RX_AGCc_LGLUT_HVAL, c=[0,1]              | 11-6  |

|-------|--------|-----------------|------------------------------------------|-------|

|       |        | 0xD0+0x200c     | RX_AGCc_GAIN_CTL, c=[0,1]                | 11-6  |

|       |        | 0xD4+0x200c     | RX_AGCc_LNA_CTL, c=[0,1]                 | 11-7  |

|       |        | 0xD8+0x200c     | RX_AGCc_LNA_DATA, c=[0,1]                | 11-8  |

|       |        | 0xDC+0x200c     | RX_AGCc_VALUE_WR, c=[0,1]                | 11-8  |

|       |        | 0xE0+0x200c     | RX_AGCc_LNA_FILT_WR, c=[0,1]             | 11-9  |

|       |        | 0xE4+0x200c     | RX_AGCc_DC_GAIN, c=[0,1]                 | 11-9  |

|       | 0xE    | 8+0x200c+4n-4   | RX_AGCc_VALUE_n_MIN, c=[0,1], n=[14]     | 11-9  |

|       |        | 0xF8+0x200c     | RX_AGCc_VALUE_MAX, c=[0,1]               | 11-10 |

|       | 0xF    | C+0x200c+4n-4   | RX_AGCc_IM_LEVELn, c=[0,1], n=[14]       | 11-10 |

|       | 0x10   | C+0x200c+4n-4   | RX_AGCc_LNA_n_FALL, c=[0,1], n=[14]      | 11-10 |

|       | 0x11   | C+0x200c+4n-4   | RX_AGCc_LNA_n_RISE, c=[0,1], n=[14]      | 11-11 |

|       | 0x12   | C+0x200c+4n-4   | RX_AGCc_LNA_n_OFFSET, c=[0,1], n=[14]    | 11-11 |

|       | 0x     | 13C+0x200c+4n   | RX_AGCc_LNA_BP_TIMER_n, c=[0,1], n=[03]  | 11-11 |

|       | 0x     | 14C+0x200c+4n   | RX_AGCc_LNA_NBP_TIMER_n, c=[0,1], n=[03] | 11-11 |

|       |        | 0x15C+0x200c    | RX_AGCc_LNA_RANGE_DELAY, c=[0,1]         | 11-12 |

|       |        | 0x160+0x200c    | RX_AGCc_SBI_CTL, c=[0,1]                 | 11-12 |

|       |        | 0x164+0x200c    | RX_AGCc_SBI_PACKET_DATA, c=[0,1]         | 11-13 |

|       |        | 0x168+0x200c    | RX_AGCc_VREF_DELAY_TIMER, c=[0,1]        | 11-13 |

|       |        | 0x16C+0x200c    | RX_AGCc_VREF_VAL, c=[0,1]                | 11-14 |

|       |        | 0x170+0x200c    | Reserved                                 | 11-14 |

|       |        | 0x174+0x200c    | RX_AGCc_1X_VALUE_RD, c=[0,1]             | 11-14 |

|       |        | 0x178+0x200c    | RX_AGCc_HDR_VALUE_RD, c=[0,1]            | 11-15 |

|       |        | 0x17C+0x200c    | RX_AGCc_1X_VGA_GAIN_RD, c=[0,1]          | 11-15 |

|       |        | 0x180+0x200c    | RX_AGCc_HDR_VGA_GAIN_RD, c=[0,1]         | 11-15 |

|       |        | 0x184+0x200c    | RX_AGCc_LNA_FILT_RD, c=[0,1]             | 11-15 |

|       |        | 0x188+0x200c    | RX_AGCc_LNA_RANGE_RD, c=[0,1]            | 11-15 |

| Searc | cher   |                 |                                          |       |

| 12.1  |        | isters          |                                          | 12-1  |

|       | 12.1.1 | Search write re | gisters                                  | 12-1  |

|       |        | 0x0000          | SRCH_ACC_PASS                            |       |

|       |        | 0x0004          | SRCH_CTL                                 | 12-2  |

|       |        | 0x0008          | SRCH_INTG_TIME                           | 12-3  |

|       |        | 0x000C          | SRCH_MASK_I                              | 12-3  |

|       |        | 0x0010          | SRCH_MASK_Q                              | 12-3  |

|       |        | 0x0014          | SRCH_MAX_SELECT                          | 12-4  |

|       |        | 0x0018          | SRCH_MAX_ENERGY                          | 12-4  |

|       |        | 0x001C          | SRCH_MAX_INDEX                           | 12-4  |

|       |        | 0x0020          | SRCH_NUM                                 | 12-5  |

|       |        |                 |                                          |       |

|    |              | 0x0024    | SRCH_OFFSET                | 12-5  |

|----|--------------|-----------|----------------------------|-------|

|    |              | 0x028     | SRCH_QOF_SEL               | 12-6  |

|    |              | 0x002C    | SRCH_SLEW                  | 12-6  |

|    |              | 0x0030    | SRCH_TH_ENERGY             | 12-7  |

|    |              | 0x0034    | SRCH_TH_TIME               | 12-7  |

|    |              | 0x0038    | SRCH_WALSH_NUM             |       |

|    |              |           | Reserved.                  |       |

|    |              | 0x003C    | SRCH_DMA_DATA<br>Reserved. |       |

|    |              | 0x0040    | SRCH DMA ERROR             |       |

|    |              | 0.0040    | Reserved.                  |       |

|    |              | 0x0044    | SRCH_POSITION              | 12-9  |

| 13 | 1X Demodulat | tor       |                            |       |

|    | 13.1 ARM reg | isters    |                            | 13-1  |

|    | 13.1.1       | RXCHIPX8  | clock registers            | 13-1  |

|    |              | 0x0000    | DEM1X_RESET                | 13-1  |

|    |              | 0x0004    | DEM1X_SYNC                 | 13-2  |

|    |              | 0x0008    | DEM1X_LATCH                | 13-2  |

|    |              | 0x000C    | DEM1X_TRACKING             | 13-3  |

|    |              | 0x0010    | DEM1X_FRAME_OFFSET         | 13-3  |

|    |              | 0x0014    | Reserved.                  | 13-3  |

|    |              | 0x0018    | DEM1X_OFFLINE              | 13-4  |

|    |              | 0x001C    | DEM1X_REF_COUNT            | 13-4  |

|    |              | 0x0020+4n | DEM1X_FINGERn, n = [0,5]   | 13-5  |

|    |              | 0x0038    | DEM1X_COMBINER_TIME_LOAD   | 13-5  |

|    |              | 0x003C    | DEM1X_ARM_COMBINER_SLAM    | 13-6  |

|    |              | 0x0040    | DEM1X_SLEW_COMBINER_TIME   | 13-6  |

|    |              | 0x0044    | DEM1X_LC_STATE_LOAD_LO     | 13-6  |

|    |              | 0x0048    | DEM1X_LC_STATE_LOAD_HI     | 13-7  |

|    |              | 0x004C    | DEM1X_ARM_LC_STATE_LOAD    | 13-7  |

|    |              | 0x0050    | DEM1X_COMBINER_TIME        | 13-7  |

|    |              | 0x0054    | DEM1X_FRAME_COUNT          | 13-8  |

|    |              | 0x0058    | DEM1X_LC_STATE_LO          | 13-8  |

|    |              | 0x005C    | DEM1X_LC_STATE_HI          | 13-8  |

|    |              | 0x0060    | DEM1X_TRAFFIC_REV_PWR_CTL  | 13-9  |

|    |              | 0x0064    | DEM1X_COMMON_REV_PWR_CTL   | 13-10 |

|    |              | 0x0068    | DEM1X_FWD_PWR_CTL_IMMED    |       |

|    |              | 0x006C    | DEM1X_FWD_PWR_CTL_FRAME    |       |

|    |              | 0x0078    | DEM1X_FREQUENCY_CTL        | 13-11 |

|    |              | 0x007C    | DEM1X_TIME_INT1_MASK       | 13-12 |

|        | 0x0080       | DEM1X_TIME_INT2_MASK13-12                    |

|--------|--------------|----------------------------------------------|

|        | 0x0084       | DEM1X_TIME_INT_PHASE13-12                    |

|        | 0x0088+8n    | DEM1X_CHn_LC_MASK_LO_IMMED, n=[0,2]13-13     |

|        | 0x008C+8n    | DEM1X_CHn_LC_MASK_HI_IMMED, n=[0,2]13-13     |

|        | 0x00A0+8n    | DEM1X_CHn_LC_MASK_LO_SPN_ROLL, n=[0,2] 13-13 |

|        | 0x00A4+8n    | DEM1X_CHn_LC_MASK_HI_SPN_ROLL, n=[0,2]13-14  |

|        | 0x00B8       | DEM1X_COMBINER_CTL                           |

|        | 0x00BC       | DEM1X_FW_CH_ENABLE_IMMED13-15                |

|        | 0x00C0       | DEM1X_FW_CH_ENABLE_FRAME13-15                |

|        | 0x00C4       | DEM1X_CHANNEL0_IMMED13-16                    |

|        | 0x00C8       | DEM1X_CHANNEL0_FRAME13-17                    |

|        | 0x00CC       | DEM1X_CHANNEL1_IMMED13-18                    |

|        | 0x00D0       | DEM1X_CHANNEL1_FRAME13-20                    |

|        | 0x00D4       | DEM1X_CHANNEL2_IMMED13-21                    |

|        | 0x00D8       | DEM1X_CHANNEL2_FRAME13-23                    |

|        | 0x00DC       | Reserved                                     |

|        | 0x00E0       | Reserved                                     |

|        | 0x00E4       | Reserved                                     |

|        | 0x00E8       | Reserved                                     |

|        | 0x00F0       | Reserved                                     |

|        | 0x00F4       | Reserved                                     |

| 13.1.2 | OFFLINE clo  | ck registers13-25                            |

|        | 0x00+0x38n   | DEM1X_Fn_PILOT_IMMED, n=[0,5]                |

|        | 0x04+0x38n   | DEM1X_Fn_DIVERSITY_IMMED, n=[0,5]13-26       |

| 0      | x08+0x38n+4m | DEM1X_Fn_WALSH_ACCm_IMMED13-27               |

|        | 0x030+0x38n  | DEM1X_Fn_HW_CH1_IMMED, n=[0,5]13-27          |

|        | 0x034+0x38n  | DEM1X_Fn_HW_CH2_IMMED, n=[0,5]13-27          |

| 0x     | 208+0x38n+4m | DEM1X_Fn_WALSH_ACCm_FRAME13-28               |

|        | 0x230+0x38n  | DEM1X_Fn_HW_CH1_FRAME, n=[0,5]13-29          |

|        | 0x234+0x38n  | DEM1X_Fn_HW_CH2_FRAME, n=[0,5]13-29          |

|        | 0x350        | Reserved                                     |

|        | 0x354        | Reserved                                     |

|        | 0x358        | Reserved                                     |

|        | 0x35C        | Reserved                                     |

|        | 0x360        | Reserved                                     |

|        | 0x364        | Reserved                                     |

|        | 0x368        | Reserved                                     |

#### 14 Deinterleaver

| 14.1 | ARM regi | sters         |                                             | 14-1  |

|------|----------|---------------|---------------------------------------------|-------|

|      | 14.1.1   | Decoder outp  | ut buffer/turbo write registers             | 14-1  |

|      |          | 0x0000        | DINT_RESET                                  | 14-1  |

|      |          | 0x0004        | DINT_CFG                                    | 14-2  |

|      |          | 0x0008 + 4w   | DINT_CHw_CFG, w=[02]                        | 14-4  |

|      |          | 0x0014        | Reserved.                                   | 14-5  |

|      |          | 0x0018        | TD_INTLV_CFG_LO                             | 14-6  |

|      |          | 0x001C        | TD_INTLV_CFG_HI                             | 14-7  |

|      |          | 0x0020        | TD_INTLV_SIZE_LO                            | 14-7  |

|      |          | 0x0024        | TD_INTLV_SIZE_HI                            | 14-8  |

|      |          | 0x 0028       | TD_PUNCT_LO                                 | 14-8  |

|      |          | 0x002C        | TD_PUNCT_HI                                 | 14-9  |

|      |          | 0x0030        | TD_PARAMS_LO                                | 14-10 |

|      |          | 0x0034        | TD_PARAMS_HI                                | 14-10 |

|      |          | 0x0038        | DINT_PKT_OFFSET                             | 14-11 |

|      |          | 0x003C        | Reserved.                                   | 14-12 |

|      |          | 0x0040        | DINT_TASK_OFFSET                            | 14-12 |

|      |          | 0x0044        | DINT_TASK_LIST                              | 14-12 |

|      |          | 0x0048        | Reserved.                                   | 14-12 |

|      |          | 0x004C        | Reserved.                                   | 14-12 |

|      |          | 0x0050        | Reserved.                                   | 14-12 |

|      |          | 0x0054        | Reserved.                                   | 14-12 |

|      |          | 0x0058        | DEC_OB_ADDR                                 | 14-12 |

|      |          | 0x005C        | Reserved.                                   | 14-13 |

|      |          | 0x0060        | DINT_OTD_CFG                                | 14-13 |

|      |          | 0x0064        | TD_MIN_LLR_THRESH                           | 14-13 |

|      |          | 0x0068        | TD_INTLV_LEN_X2                             | 14-14 |

|      |          | 0x006C        | TD_INTLV_LEN_X4                             | 14-14 |

|      |          | 0x0070        | TD_INTLV_LEN_X8                             | 14-15 |

|      |          | 0x0074        | TD_NUM_SLWIN_X2                             | 14-15 |

|      |          | 0x0078        | TD_NUM_SLWIN_X4                             | 14-15 |

|      |          | 0x007C        | TD_NUM_SLWIN_X8                             | 14-16 |

|      | 14.1.2   | Deinterleaver | /decoder output buffer/turbo read registers | 14-16 |

|      |          | 0x0000        | DEINT_TASK_STATUS                           | 14-16 |

|      |          | 0x0004        | Reserved.                                   | 14-17 |

|      |          | 0x0008        | VD_DONE_STATUS                              | 14-17 |

|      |          | 0x000C        | TD_DONE_STATUS                              | 14-17 |

|      |          | 0x0010        | DEC_OB_DATA                                 | 14-17 |

| <b>15</b> | SVD  |             |            |                                       |      |

|-----------|------|-------------|------------|---------------------------------------|------|

|           | 15.1 | ARM reg     | isters     |                                       | 15-1 |

|           |      |             | 0x0000     | VD_RESET                              | 15-1 |

|           |      |             | 0x0004     | VD_MODE                               | 15-2 |

|           |      |             | 0x0008     | VD_POLY2IJ                            | 15-2 |

|           |      |             | 0x000C     | VD_POLY3IJ                            | 15-3 |

|           |      |             | 0x0010     | VD_POLY3K                             | 15-3 |

|           |      |             | 0x0014     | VD_POLY4IJ                            | 15-3 |

|           |      |             | 0x0018     | VD_POLY4KL                            | 15-4 |

| 16        |      |             | -          | uffer / Output Buffer                 |      |

|           | 16.1 |             |            |                                       |      |

|           | 16.2 | ARM reg     | isters     |                                       |      |

|           |      |             | 0x0000     | Reserved                              |      |

|           |      |             | 0x0004     | Reserved                              |      |

|           |      |             | 0x0008     | Reserved                              |      |

|           |      |             | 0x000C     | Reserved                              |      |

|           |      | 16.2.1      | Output buf | fer                                   |      |

|           |      |             | 0x0010     | HDR_DEC_OB_RESET                      |      |

|           |      |             | 0x0020     | HDR_DEC_OB_HUNT_CHAR                  |      |

|           |      |             | 0x0024     | HDR_DBIF_WATERMARK                    |      |

|           |      |             | 0x0028     | HDR_DBIF_PACKET_CNT                   |      |

|           |      |             | 0x002C     | HDR_DBIF_STALE_TIMEOUT                |      |

|           |      |             | 0x0030     | Reserved                              |      |

|           |      |             | 0x0034     | Reserved                              |      |

|           |      |             | 0x0038     | Reserved                              |      |

|           |      |             | 0x003C     | Reserved                              | 16-3 |

|           |      |             | 0x0040     | Reserved                              |      |

|           |      |             | 0x0044     | Reserved                              | 16-3 |

|           |      |             | 0x0048     | Reserved                              | 16-4 |

|           |      | 16.2.2      | Output buf | fer frame header                      | 16-4 |

|           |      |             | 0x0000     | HDR_FRAME_HEADER_0                    | 16-4 |

|           |      |             | 0x0000     | HDR_FRAME_HEADER_1                    | 16-5 |

|           |      |             | 0x0000     | HDR_FRAME_HEADER_2                    |      |

|           | 16.3 | Application | on notes   |                                       | 16-6 |

|           |      | 16.3.1      | Symbol bu  | ffer                                  | 16-6 |

|           |      |             | 16.3.1.1   | FTT table loading                     | 16-6 |

|           |      | 16.3.2      | Decoder or | utput buffer                          |      |

|           |      |             | 16.3.2.1   | Interrupt generation in the DBIF mode | 16-7 |

|           |      |             | 16.3.2.2   | Software procedure                    | 16-7 |

#### 17 Modulator

| 17.1 | Overview |               |                                            | 17-1  |

|------|----------|---------------|--------------------------------------------|-------|

|      | 17.1.1   | Shared regist | ers of 1X and HDR                          | 17-1  |

| 17.2 | ARM regi |               |                                            |       |

|      | 17.2.1   | 1X Modulato   | r software registers                       | 17-3  |

|      |          | 17.2.1.1      | 1X modulator functional software registers | 17-3  |

|      |          | 0x0000        | MOD_MODE                                   | 17-3  |

|      |          | 0x0004        | MOD_PRMBL_GAIN                             | 17-3  |

|      |          | 0x0008        | MOD_RESET                                  | 17-3  |

|      |          | 0x000C        | MOD_CH1_TIMING_CTL                         | 17-4  |

|      |          | 0x0010        | MOD_CH2_TIMING_CTL                         | 17-4  |

|      |          | 0x0014        | MOD_CH3_TIMING_CTL                         | 17-4  |

|      |          | 0x0018 +4w    | Reserved.                                  | 17-5  |

|      |          | 0x0020 + 4w   | Reserved.                                  | 17-5  |

|      |          | 0x0028        | U_PN_STATE_0                               | 17-5  |

|      |          | 0x002C        | U_PN_STATE_1                               | 17-5  |

|      |          | 0x0030        | U_PN_STATE_2                               | 17-5  |

|      |          | 0x0034        | U_PN_STATE_3                               | 17-6  |

|      |          | 0x0038        | U_PN_STATE_4                               | 17-6  |

|      |          | 0x003C        | U_PN_STATE_5                               | 17-6  |

|      |          | 0x0040 + 4w   | U_PN_MASK_w, w=[05]                        | 17-7  |

|      |          | 0x0058        | FRAME_OFF                                  | 17-8  |

|      |          | 0x005C        | PA_WARMUP                                  | 17-9  |

|      |          | 0x0060        | MOD_STMR_MODIFIER_0                        | 17-9  |

|      |          | 0x0064        | MOD_STMR_MODIFIER_1                        | 17-10 |

|      |          | 0x0068        | MOD_STMR_CMD                               | 17-10 |

|      |          | 0x006C        | ENC_INT_ST                                 | 17-11 |

|      |          | 0x0070        | MOD_CH1_ENC_CTL                            | 17-11 |

|      |          | 0x0074        | MOD_CH1_ENC_DATA                           | 17-12 |

|      |          | 0x0078        | MOD_CH1_CRC_POLY                           | 17-13 |

|      |          | 0x007C        | MOD_CH1_PUNCT_PATN_1                       | 17-13 |

|      |          | 0x0080        | MOD_CH1_PUNCT_PATN_0                       | 17-14 |

|      |          | 0x0084        | MOD_CH2_ENC_CTL_0                          | 17-14 |

|      |          | 0x0088        | MOD_CH2_ENC_CTL_1                          | 17-16 |

|      |          | 0x008C        | MOD_CH2_ENC_DATA                           | 17-16 |

|      |          | 0x0090        | MOD_CH2_CRC_POLY                           | 17-17 |

|      |          | 0x0094        | MOD_CH2_PUNCT_PATN_1                       | 17-17 |

|      |          | 0x0098        | MOD_CH2_PUNCT_PATN_0                       | 17-18 |

|      |          | 0x009C        | MOD_CH3_ENC_CTL_0                          | 17-18 |

|      |          | 0x00A0        | MOD_CH3_ENC_CTL_1                          | 17-19 |

| 0x00A4       | MOD_CH3_ENC_DATA               | 17-21  |

|--------------|--------------------------------|--------|

| 0x00A8       | MOD_CH3_CRC_POLY               | 17-21  |

| 0x00AC       | MOD_CH3_PUNCT_PATN_1           | 17-22  |

| 0x00B0       | MOD_CH3_PUNCT_PATN_0           | 17-22  |

| 0x00B4       | MOD_SCH_LTU_CTL                | 17-23  |

| 0x00B8       | MOD_MISC_CTL                   | 17-23  |

| 0x00BC       | MOD_PCH_GAIN                   | 17-25  |

| 0x00C0       | MOD_DCCH_GAIN                  | 17-25  |

| 0x00C4       | MOD_FCH_GAIN                   | 17-26  |

| 0x00C8       | MOD_SCH_GAIN                   | 17-26  |

| 0x00CC       | MOD_PRMBL_CTL_0                | 17-26  |

| 0x00D0       | MOD_PRMBL_CTL_1                | 17-27  |

| 0x00D4       | MOD_ROTATOR_MAP                | 17-27  |

| 0x00D8       | MOD_WSYM_STATE                 | 17-28  |

| 0x00DC       | TX_VERY_EARLY_FRAME_CTL        | 17-28  |

| 0x00E0       | TX_2_EARLY_PCG_CTL             | 17-29  |

| 0x00E4       | MOD_PCH_PCBIT_DATA             | 17-29  |

| 0x00E8       | MOD_PCH_PCBIT_MASK             | 17-29  |

| 0x00EC       | MOD_WCOVER_SEL                 | 17-30  |

| 0x00F0       | TX_WARMUP                      | 17-30  |

| 0x0228       | MOD_STATUS                     | 17-31  |

| 0x0224       | MASK_DATA                      | 17-32  |

| 0x020C       | Reserved.                      | 17-32  |

| 0x0220       | Reserved.                      | 17-32  |

| 0x0110       | Reserved.                      | 17-32  |

| 0x0114       | Reserved.                      | 17-32  |

| 0x0118       | Reserved.                      | 17-32  |

| 0x011C       | Reserved.                      | 17-32  |

| 0x022C       | Reserved.                      | 17-32  |

| HDR Modulato | or software registers          | .17-33 |

| 0x0120       | REVMOD_TIME_STAMP_CTL          | 17-33  |

| 0x023C       | REVMOD_TIME_STAMP              | 17-33  |

| 0x0240       | REVMOD_TIME_STAMP2             | 17-33  |

| 0x0124       | REVMOD_SLOT_INT_OFFSET         | 17-34  |

| 0x0128       | REVMOD_FRAME_OFFSET            | 17-34  |

| 0x012C       | REVMOD_MOD_CTL                 | 17-34  |

| 0x0130       | REVMOD_TENC_CTL                | 17-35  |

| 0x0234       | REVMOD_TENC_STATUS             | 17-35  |

| 0x0134       | REVMOD_RRI_REQUEST             | 17-36  |

| 0x0138+4w    | REVMOD_PN_LONG_STATE_w, w=[02] | 17-37  |

17.2.2

|        | 0x0144+4w  | REVMOD_PN_I_LONG_MASK_w, w=[02] | 17-38 |

|--------|------------|---------------------------------|-------|

|        | 0x0150+4w  | REVMOD_PN_Q_LONG_MASK_w, w=[02] | 17-39 |

|        | 0x015C     | REVMOD_PN_CTL                   | 17-39 |

|        | 0x0160     | REVMOD_PA_CTL                   | 17-40 |

|        | 0x0164     | REVMOD_FRM_CNT_OFFSET           | 17-42 |

|        | 0x0168     | REVMOD_FRM_CNT_OFFSET_CTL       | 17-42 |

|        | 0x016C     | REVMOD_PA_WARMUP                | 17-42 |

|        | 0x0208     | REVMOD_TX_WARMUP                | 17-43 |

|        | 0x0170     | REVMOD_ENC_MODE                 | 17-43 |

|        | 0x0174     | REVMOD_EDI_CONTROL              | 17-43 |

|        | 0x0178     | REVMOD_EDI_DATA                 | 17-44 |

|        | 0x017C     | REVMOD_ENC_RATE                 | 17-44 |

|        | 0x0210     | REVMOD_TX_TIME_LATCH            | 17-45 |

|        | 0x0238     | REVMOD_TX_TIME_RD               | 17-45 |

| 17.2.3 | Tx AGC sof | tware registers                 |       |

|        | 17.2.3.1   | Tx AGC software write registers | 17-46 |

|        | 0x0180     | TX_AGC_CTL                      | 17-46 |

|        | 0x0184     | TX_AGC_CTL2                     | 17-48 |

|        | 0x0188     | TX_AGC_RESET                    | 17-49 |

|        | 0x018C     | Reserved.                       | 17-49 |

|        | 0x0190     | AGC_TX_MASK_DATA_SEL            | 17-49 |

|        | 0x0194     | AGC_TX_RCCCH_FRAME_DELAY        | 17-49 |

|        | 0x0198     | PA_R_MAP                        | 17-50 |

|        | 0x019C     | PA_R_TIMER                      | 17-50 |

|        | 0x01A0     | PA_R1_FALL                      | 17-50 |

|        | 0x01A4     | PA_R1_RISE                      | 17-51 |

|        | 0x01A8     | PA_R2_FALL                      | 17-51 |

|        | 0x01AC     | PA_R2_RISE                      | 17-51 |

|        | 0x01B0     | PA_R3_FALL                      | 17-51 |

|        | 0x01B4     | PA_R3_RISE                      |       |

|        | 0x01B8+4w  | PA_Sw_OFFSET, w=[03]            | 17-52 |

|        | 0x01C8     | Reserved.                       | 17-52 |

|        | 0x01CC     | RAS_RAM_WR_ADDR_RESET           | 17-52 |

|        | 0x01D0     | RAS_RAM_DATA                    | 17-53 |

|        | 0x01D4     |                                 |       |

|        | 0x01D8     | TX_AGC_ADJ_WR                   | 17-53 |

|        | 0x01DC     | TX_ALIGN_DELAY                  | 17-53 |

|        | 0x01E0     | TX_ATTEN_LIMIT_WR               | 17-54 |

|        | 0x01E4     | TX_GAIN_ADJ_WR                  | 17-54 |

|        | 0x01E8     | TX GAIN LIMIT WR                | 17-55 |

|        | 0x01EC    | TX_GAIN_CTL_LATCH                       | 17-55 |

|--------|-----------|-----------------------------------------|-------|

|        | 0x01F0    | TX_OPEN_LOOP_WR                         | 17-55 |

|        | 0x01F4    | TX_PDM_DELAY_VAL                        | 17-55 |

|        | 0x01F8    | TX_RATE_ADJ                             | 17-56 |

|        | 0x01FC    | Reserved                                | 17-56 |

|        | 0x0200    | Reserved                                | 17-56 |

|        | 0x0204    | Reserved                                | 17-56 |

|        | 17.2.3.2  | Tx AGC software read registers          | 17-56 |

|        | 0x0244    | TX_PA_RD                                | 17-56 |

|        | 0x0230    | RATCHET_BIT_DIS                         | 17-57 |

|        | 0x0198    | TX_AGC_ADJ_RD                           | 17-57 |

|        | 0x0214    | TX_GAIN_ADJ_RD                          | 17-57 |

|        | 0x0218    | TX_GAIN_CTL_RD                          | 17-58 |

|        | 0x021C    | TX_OPEN_LOOP_RD                         | 17-58 |

| 17.2.4 | Modulator | Firmware registers                      | 17-59 |

|        | 17.2.4.1  | HDR modulator firmware registers        | 17-59 |

|        | 0x000     | REVMOD_DRC_CODE_INDEX                   | 17-59 |

|        | 0x0004    | REVMOD_DRC_WALSH_COVER                  | 17-60 |

|        | 0x0008    | REVMOD_RF_PN_ROT                        | 17-60 |

|        | 0x000C    | REVMOD_PDM_CTL                          | 17-61 |

|        | 0x0010    | REVMOD_TX_AGC_ODRIVE_DLY                | 17-62 |

|        | 0x0014    | REVMOD_TX_AGC_ADJ                       | 17-63 |

|        | 0x0018    | REVMOD_PDM0                             | 17-63 |

|        | 0x001C    | REVMOD_PDM1                             | 17-64 |

|        | 0x0020    | REVMOD_RF_PN_ROLL_TIME                  | 17-64 |

|        | 0x0024    | REVMOD_PA_RANGE                         | 17-64 |

|        | 0x0028    | REVMOD_RATE_INDEX                       | 17-65 |

|        | 0x002C    | REVMOD_PA_RANGE_POLARITY                | 17-66 |

|        | 0x0030    | REVMOD_I_GAIN_PILOT                     | 17-66 |

|        | 0x0034    | REVMOD_I_GAIN_ACK                       | 17-66 |

|        | 0x0038    | REVMOD_ACK_CTL                          | 17-67 |

|        | 0x003C    | REVMOD_PA_POWERUP_CTL                   | 17-67 |

|        | 0x0040    | REVMOD_PA_RANGE_DELAY                   | 17-67 |

|        | 0x0044    | REVMOD_Q_GAIN_TRAFFIC                   | 17-67 |

|        | 0x0048    | REVMOD_Q_GAIN_DRC                       |       |

|        | 17.2.4.2  | Tx AGC power control firmware registers | 17-68 |

|        | 0x004C    | REV_LINKPWR_CTRL_WR                     | 17-68 |

### 18 Sleep Controller

| 18.1 | ARM registers |                                  | 18-1  |

|------|---------------|----------------------------------|-------|

|      | 0x0000        | SLEEP_CTL                        | 18-1  |

|      | 0x0004        | SLEEP_CMD                        | 18-2  |

|      | 0x0008        | SLEEP_CX8_EXPIRE                 | 18-2  |

|      | 0x000C        | SLEEP_CX8_COUNT                  | 18-2  |

|      | 0x0010        | SLEEP_COUNT                      | 18-2  |

|      | 0x0014        | SLEEP_STATUS                     | 18-3  |

|      | 0x0018        | HDR_SLEEP_CTL                    | 18-3  |

|      | 0x001C        | HDR_SLEEP_CMD                    | 18-3  |

|      | 0x0020        | HDR_SLEEP_CX8_EXPIRE             | 18-4  |

|      | 0x0024        | HDR_SLEEP_CX8_COUNT              | 18-4  |

|      | 0x0028        | HDR_SLEEP_COUNT                  | 18-4  |

|      | 0x002C        | HDR_SLEEP_STATUS                 | 18-5  |

|      | 0x0030        | SLEEP_XTAL_TIMER_COUNT           | 18-5  |

|      | 0x0034        | SLEEP_XTAL_TIMETICK_COUNT        | 18-5  |

|      | 0x0038        | SLEEP_XTAL_FREQ_ERR              | 18-6  |

|      | 0x003C        | WDOG_RESET                       | 18-6  |

|      | 0x0040        | AUTOKICK_START                   | 18-6  |

|      | 0x0044        | WDOG_STATUS                      | 18-7  |

|      | 0x0048        | WDOG_WAKEUP_CTL                  | 18-7  |

|      | 0x004C        | GSM_SLEEP_CTL                    | 18-8  |

|      | 0x0050        | GSM_SLEEP_WU_0_TIME_CONFIG       | 18-8  |

|      | 0x0054        | GSM_SLEEP_PHASE_CORRECTION_CNT   | 18-9  |

|      | 0x0058        | GSM_SLEEP_WU_0_CONFIG            | 18-9  |

|      | 0x005C        | GSM_SLEEP_WU_1_CONFIG            | 18-10 |

|      | 0x0060        | GSM_SLEEP_INT_STATUS_RD          | 18-11 |

|      | 0x0064        | GSM_SLEEP_INT_CLEAR_WR           | 18-12 |

|      | 0x0068        | GSM_SLEEP_INT_ENABLE             | 18-12 |

|      | 0x006C        | GSM_SLEEP_ON_LINE_TIME_CONFIG    | 18-12 |

|      | 0x0070        | GSM_SLEEP_WU_1_TIME_CONFIG       | 18-13 |

|      | 0x0074        | GSM_SLEEP_WU_0_ACT_TIME_0_CONFIG | 18-13 |

|      | 0x0078        | GSM_SLEEP_WU_0_ACT_TIME_1_CONFIG | 18-13 |

|      | 0x007C        | GSM_SLEEP_WU_1_ACT_TIME_0_CONFIG | 18-14 |

|      | 0x0080        | GSM_SLEEP_WU_1_ACT_TIME_1_CONFIG | 18-14 |

|      | 0x0084        | GSM_SLEEP_WU_1_ACT_TIME_2_CONFIG | 18-14 |

|      | 0x0088        | GSM_SLEEP_WU_1_ACT_TIME_3_CONFIG | 18-15 |

|      | 0x008C        | GSM_SLEEP_WU_1_ACT_TIME_4_CONFIG | 18-15 |

|      | 0x0090        | GSM_SLEEP_WU_1_ACT_TIME_5_CONFIG | 18-16 |

|      | 0x0094        | SLEEP_WAKEUP_STATUS              | 18-16 |

|    |      |         | 0x0098         | SLEEP_WAKEUP                         | 18-16 |

|----|------|---------|----------------|--------------------------------------|-------|

|    |      |         | 0x009C         | SLEEP_EXPIRE_STATUS                  | 18-17 |

|    |      |         | 0x00A0         | SLEEP_EXPIRE                         | 18-17 |

|    |      |         | 0x00A4         | HDR_SLEEP_WAKEUP_STATUS              | 18-17 |

|    |      |         | 0x00A8         | HDR_SLEEP_WAKEUP                     | 18-17 |

|    |      |         | 0x00AC         | HDR_SLEEP_EXPIRE_STATUS              | 18-18 |

|    |      |         | 0x00B0         | HDR_SLEEP_EXPIRE                     | 18-18 |

|    |      |         | 0x00B4         | SLEEP_XTAL_TIMER_ENABLE              | 18-18 |

|    |      |         | 0x00B8         | SLEEP_XTAL_TIMER_MATCH_VAL           | 18-19 |

|    |      |         | 0x00BC         | SLEEP_XTAL_TIMETICK_MATCH_VAL_STATUS | 18-19 |

|    |      |         | 0x00C0         | SLEEP_XTAL_TIMETICK_MATCH_VAL        | 18-19 |

|    |      |         | 0x00C4         | SLEEP_XTAL_COUNT                     | 18-20 |

|    |      |         | 0x00C8         | WDOG_EXPIRED_WIDTH                   | 18-20 |

|    |      |         | 0x00CC         | WDOG_TEST_LOAD_STATUS                | 18-20 |

|    |      |         | 0x00D0         | WDOG_TEST_LOAD                       | 18-20 |

|    |      |         | 0x00D4         | WDOG_TEST                            | 18-21 |

|    |      |         | 0x00D8         | GSM_SLEEP_INTERVAL                   | 18-21 |

| 19 | USB  |         |                |                                      |       |

| 19 | 19.1 | APM rog | istors         |                                      | 10 1  |

|    | 19.1 | 19.1.1  |                | sters                                |       |

|    |      | 19.1.1  | 0x000          | USB_HARDWARE_MODE                    |       |

|    |      |         | 0x000          | USB_CORE_INT_STATUS                  |       |

|    |      |         | 0x004<br>0x008 | USB_CORE_INT_ENA                     |       |

|    |      |         | 0x00C          | USB_CLOCK_CTL                        |       |

|    |      |         | 0x00C          | USB_RESET_CTL                        |       |

|    |      |         | 0x010<br>0x014 | USB_FRAME_INTERVAL                   |       |

|    |      |         | 0x014<br>0x018 | USB_FRAME_REMAINING_BIT_WIDTH        |       |

|    |      |         | 0x01C          | USB_HNP_CTL_STATUS                   |       |

|    |      |         | 0x020          | USB HNP TIMERS1                      |       |

|    |      |         | 0x024          | USB HNP TIMERS2                      |       |

|    |      |         | 0x028          | USB_HNP_TIMER3_PULSE_CTL             |       |

|    |      |         | 0x02C          | USB_HNP_INT_STATUS                   |       |

|    |      |         | 0x030          | USB_HNP_INT_ENA                      |       |

|    |      | 19.1.2  |                |                                      |       |

|    |      | 191112  | 0x $0$ 8 $0$   | USB_HOST_CTL                         |       |

|    |      |         | 0x088          | USB_H_SYSTEM_INT_STATUS              |       |

|    |      |         | 0x08C          | USB_H_SYSTEM_INT_ENA                 |       |

|    |      |         | 0x098          | USB_H_X_BUFFER_INT_STATUS            |       |

|    |      |         | 0x09C          | USB_H_Y_BUFFER_INT_STATUS            |       |

|    |      |         |                |                                      |       |

|        | 0x0A0         | USB_H_XY_INT_ENA                           | 19-21 |

|--------|---------------|--------------------------------------------|-------|

|        | 0x0A8         | USB_H_X_FILLED_STATUS                      | 19-22 |

|        | 0x0AC         | USB_H_Y_FILLED_STATUS                      | 19-22 |

|        | 0x0C0         | USB_ETD_ENA                                | 19-22 |

|        | 0x0C4         | USB_ETD_ENA_CLEAR                          | 19-23 |

|        | 0x0CC         | USB_H_IMMEDIATE_INT                        | 19-23 |

|        | 0x0D0         | USB_H_ETD_DONE_STATUS                      | 19-24 |

|        | 0x0D4         | USB_ETD_DONE_ENA                           | 19-24 |

|        | 0x0E0         | USB_H_FRAME_NUMBER                         | 19-25 |

|        | 0x0E4         | USB_LOW_SPEED_THRESH                       | 19-25 |

|        | 0x0E8         | USB_ROOT_HUB_DESCRIPTOR_A                  | 19-26 |

|        | 0x0EC         | USB_ROOT_HUB_DESCRIPTOR_B                  | 19-27 |

|        | 0x0F0         | USB_ROOT_HUB_STATUS                        | 19-27 |

|        | 0x0F4+4n      | USB_PORT_STATUS_ <i>n</i> , <i>n</i> =[02] | 19-28 |

| 19.1.3 | Function regi | isters                                     | 19-31 |

|        | 0x040         | USB_FUNCTION_CMD_STATUS                    | 19-32 |

|        | 0x044         | USB_DEVICE_ADDRESS                         | 19-33 |

|        | 0x048         | USB_F_SYSTEM_INT_STATUS                    | 19-33 |

|        | 0x04C         | USB_F_SYSTEM_INT_ENA                       | 19-34 |

|        | 0x050         | USB_F_X_BUFFER_INT_STATUS                  | 19-35 |

|        | 0x054         | USB_F_Y_BUFFER_INT_STATUS                  | 19-37 |

|        | 0x058         | USB_F_XY_INT_ENA                           | 19-38 |

|        | 0x05C         | USB_F_X_FILLED_STATUS                      | 19-40 |

|        | 0x060         | USB_F_Y_FILLED_STATUS                      | 19-41 |

|        | 0x064         | USB_ENDPOINT_ENA                           | 19-43 |

|        | 0x068         | USB_ENDPOINT_READY                         | 19-45 |

|        | 0x06C         | USB_F_IMMEDIATE_INT                        | 19-46 |

|        | 0x070         | USB_F_ENDPOINT_DONE_STATUS                 | 19-48 |

|        | 0x074         | USB_ENDPOINT_DONE_ENA                      | 19-50 |

|        | 0x078         | USB_ENDPOINT_TOGGLE_BITS                   | 19-52 |

|        | 0x07C         | USB_F_FRAME_NUMBER                         | 19-53 |

|        | 0x07C         | USB_ENDPOINT_READY_CLR                     | 19-54 |

| 19.1.4 | DMA registe   | rs                                         | 19-54 |

|        | 0x0800        | USB_DMA_REVISION                           | 19-54 |

|        | 0x0804        | USB_DMA_INT_STATUS                         | 19-54 |

|        | 0x0808        | USB_DMA_INT_ENA                            | 19-55 |

|        | 0x080c        | USB_ETD_DMA_ERROR_STATUS                   | 19-55 |

|        | 0x0810        | USB_EP_DMA_ERROR_STATUS                    | 19-56 |

|        | 0x0820        | USB_ETD_DMA_ENA                            | 19-56 |

|        | 0x0824        | USB EP DMA ENA                             | 19-56 |

|    | 21.1 | ARM regis | sters                          |                                                                                | 21-1  |

|----|------|-----------|--------------------------------|--------------------------------------------------------------------------------|-------|

| 21 | •    | herals    |                                |                                                                                | 01.1  |

|    |      |           | UAU24 FUAJUII                  | 05/1CH_COM 10_0, H=[0,1]                                                       | 20-13 |

|    |      |           | 0x030+0x30n $0x024+0x30n$      | GSACn_CONFIG_0, n=[0,1]                                                        |       |

|    |      |           | 0x04C + 0x30n<br>0x050 + 0x30n | AMBA_KEY_STRMn_BLK2_WORD2_RD, n=[0,1] AMBA_KEY_STRMn_BLK2_WORD3_RD, n=[0,1]    |       |

|    |      |           | 0x048+0x30n<br>0x04C+0x30n     | AMBA_KEY_STRMn_BLK2_WORD1_RD, n=[0,1]<br>AMBA_KEY_STRMn_BLK2_WORD2_RD, n=[0,1] |       |

|    |      |           | 0x044+0x30n                    |                                                                                |       |

|    |      |           | 0x040+0x30n                    | AMBA_KEY_STRMn_BLK1_WORD3_RD, n=[0,1]  AMBA_KEY_STRMn_BLK2_WORD0_RD, n=[0,1]   |       |

|    |      |           |                                | AMBA_KEY_STRMn_BLK1_WORD2_RD, n=[0,1] AMBA_KEY_STRMn_BLK1_WORD3_RD, n=[0,1]    |       |

|    |      |           | 0x038+0x30n<br>0x03C+0x30n     | AMBA_KEY_STRMn_BLK1_WORD1_RD, n=[0,1]                                          |       |

|    |      |           | 0x034+0x30n                    | AMBA_KEY_STRMn_BLK1_WORD0_RD, n=[0,1]                                          |       |

|    |      | 20.2.2    |                                | S                                                                              |       |

|    |      | 20.2.2    | 0x0024                         | ENABLE_GSTMR_DURING_SLEEP                                                      |       |

|    |      |           | 0x0020                         | GSM_TIME_LOAD_CTL_CMD                                                          |       |

|    |      |           | 0x001C                         | GSM_CORE_MICRO_RESET_REG                                                       |       |

|    |      |           | 0x0018                         | GSM_TIME_TC_ADJ_CMD                                                            |       |

|    |      |           | 0x0014                         | GSM_DSP_WR_CLK_CTL                                                             |       |

|    |      |           | 0x0010                         | VFR_IRQ_ALIGN_CMD                                                              |       |

|    |      |           | 0x000C                         | MICRO_IRQ_CONFIG_RW                                                            |       |

|    |      |           | 0x0008                         | GO_TO_SLEEP_CMD.                                                               |       |

|    |      |           | 0x0004                         | MICRO_GSM_TIME_RD                                                              |       |

|    |      | 20.2.1    |                                | gisters                                                                        |       |

|    | 20.2 |           |                                |                                                                                |       |

|    | 20.1 |           |                                |                                                                                |       |

| 20 |      | Core      |                                |                                                                                |       |

|    |      |           |                                | , , , , , , , , , , , , , , , ,                                                |       |

|    |      |           | 0x0a80+4n                      | USB_EPn_DMA_BUFFER_XFER_PTR, n=[031]                                           |       |

|    |      |           | 0x0a00+4n                      | USB_ETDn_DMA_BUFFER_XFER_PTR, n=[031]                                          |       |

|    |      |           | 0x980+4n                       | USB_EPn_SYS_MEM_START_ADDR, n=[031]                                            |       |

|    |      |           | 0x900+4n                       | USB_ETDn_SYS_MEM_START_ADDR, n=[031]                                           |       |

|    |      |           | 0x84C                          | USB EP DMA CHANNEL CLEAR                                                       |       |

|    |      |           | 0x848                          | USB_ETD_DMA_CHANNEL_CLEAR                                                      |       |

|    |      |           | 0x0830                         | USB_MISC_CTL                                                                   |       |

|    |      |           | 0x083c                         | USB_EP_DMA_BURST4_ENA                                                          |       |

|    |      |           | 0x0834<br>0x0838               | USB_ETD_DMA_BURST4_ENA                                                         |       |

|    |      |           | 0x0830<br>0x0834               | USB_ETD_DMA_ENB_XY_TRIG_REQUSB_EP_DMA_ENA_XY_TRIGER_REQ                        |       |

|    |      |           | 0x082c                         | USB_EP_DMA_ENA_X_TRIGER_REQ                                                    |       |

|    |      |           | 0x0828                         | USB_ETD_DMA_ENA_X_TRIGER_REQ                                                   |       |

|    |      |           | 0.0028                         | LICE ETD DMA ENA V TDICED DEC                                                  | 10.57 |

| 21.1.1.1 | System registers                    | 21-2  |

|----------|-------------------------------------|-------|

| 0x0004   | CHIP_MODE                           | 21-2  |

| 0x0008   | SYSTEM_MODE                         | 21-2  |

| 21.1.1.2 | Peripherals miscellaneous registers | 21-4  |

| 0x0010   | WEB_MISC_WR                         | 21-4  |

| 0x0014   | WEB_MISC2_WR                        | 21-5  |

| 0x0018   | WEB_MISC_RD                         | 21-7  |

| 21.1.1.3 | RF control registers                | 21-7  |

| 0x001C   | PA_ON_CTL                           | 21-7  |

| 0x0020   | PA_ON_STATUS                        |       |

| 21.1.1.4 | Codec read registers                | 21-9  |

| 0x0024   | Reserved.                           | 21-9  |

| 0x0028   | Reserved.                           |       |

| 21.1.1.5 | PAD registers                       | 21-9  |

| 0x002C   | PAD_PUPD_EN                         | 21-9  |

| 0x0030   | PAD_PUPD_N                          | 21-10 |

| 0x0034   | PAD_HDRIVE_SEL_0                    | 21-11 |

| 0x0038   | PAD_HDRIVE_SEL_1                    | 21-11 |

| 0x003C   | PAD_HDRIVE_SEL_2                    |       |

| 21.1.1.6 | Analog-die control register         | 21-14 |

| 0x0040   | SLEEP_N_ADIE                        | 21-14 |

| 0x0044   | Reserved.                           | 21-14 |

| 0x0048   | Reserved.                           | 21-14 |

| 0x004C   | Reserved.                           |       |

| 21.1.1.7 | AUX/CODEC interface registers       | 21-15 |

| 0x0050   | CODEC_CTL                           | 21-15 |

| 0x0054   | PCM_PATH_CTL                        |       |

| 21.1.1.8 | I <sup>2</sup> C registers          | 21-17 |

| 0x0060   | I2C_WRITE_DATA                      | 21-17 |

| 0x0064   | I2C_CLK_CTL                         | 21-18 |

| 0x0068   | I2C_STATUS                          | 21-19 |

| 0x006C   | I2C_READ_DATA                       | 21-20 |

| 0x0070   | USB_PIN_CONFIG                      | 21-20 |

| 0x0074   | USB_PIN_SEL                         | 21-20 |

| 0x0078   | Reserved.                           | 21-21 |

|          | ck registers                        |       |

| 21.1.2.1 | PDM0, PDM1, and PDM2 registers      | 21-21 |

| 0x0000   | TCXO_PDM_CTL                        |       |

| 0x0004   | PDM0_CTL                            | 21-22 |

| 0x0008   | PDM1_CTL                            | 21-23 |

21.1.2

|    |      |           | 0x000C         | PDM2_CTL                       | 21-23 |

|----|------|-----------|----------------|--------------------------------|-------|

|    |      |           |                | Reserved                       |       |

|    |      |           |                | Reserved                       |       |

|    |      |           | 21.1.2.2       | Ringer registers               |       |

|    |      |           | 0x001C         | Reserved                       | 21-24 |

|    |      |           | 0x0020         | Reserved                       | 21-24 |

|    |      |           | 0x0024         | RINGER_MN_A_MDIV               | 21-24 |

|    |      |           | 0x0030         | RINGER_MN_B_MDIV               | 21-25 |

|    |      |           | 21.1.2.3       | Timetick registers             | 21-25 |

|    |      |           | 0x0034         | TIME_TICK_CTL                  | 21-25 |

|    |      |           | 0x0038         | TIME_TICK_INT_MSB              | 21-26 |

| 22 | SBI  |           |                |                                |       |

|    | 22.1 | SBI overv | iew            |                                | 22-1  |

|    | 22.2 | ARM regi  | sters          |                                | 22-2  |

|    |      | 22.2.1    | Write register | 'S                             | 22-2  |

|    |      |           | 0x000+0x40c    | SBIc_CLK_CTL, c=[0,1]          | 22-2  |

|    |      |           | 0x004+0x40c    | SBIc_CTL, c=[0,1]              | 22-3  |

|    |      |           | 0x008+0x40c    | SBIc_BYPASS_WR, c=[0,1]        | 22-5  |

|    |      |           | 0x00C+0x40c    | SBIc_WR, c=[0,1]               | 22-6  |

|    |      |           | 0x010+0x40c    | SBIc_START_CTL, c=[0,1]        | 22-6  |

|    |      |           | 0x014+0x40c    | SBIc_SECOND_IDCODE, c=[0,1]    | 22-6  |