# E2 Quad-Band GPRS / EDGE Smart Phone LEVEL 3 CIRCUIT DESCRIPTION

# Service Engineering & Optimization

# E2 Level 3 Circuit Description

| 1 | Rev   | ision His | story                                   | . 8 |

|---|-------|-----------|-----------------------------------------|-----|

| 2 | Intro | oduction  | and Purpose                             | . 9 |

| 3 | PCA   | AP2 Hard  | lware Overview                          | . 9 |

|   | 3.1   | Power N   | Management                              | 10  |

|   | 3     | .1.1 Reg  | ulator Usage Description                | 10  |

|   | 3     | .1.2 Pow  | ver Distribution Tree                   | 13  |

|   | 3     | .1.3 E2 H | Power Management Control                | 14  |

|   | 3     | .1.4 E2 A | Audio Routing and SPI Control           | 15  |

|   | 3.2   | E2 Aud    | io System and PCAP2 Audio Section       | 16  |

|   | 3     | .2.1 E2 A | Audio System Architecture Block Diagram | 16  |

|   | 3     | .2.2 Aud  | lio Input Section                       | 22  |

|   | 3     | .2.3 Aud  | lio Output Section                      | 23  |

|   | 3.3   | A/D Co    | nversion And Channel Allocations        | 24  |

|   | 3     | .3.2 Deta | ailed Description Of Each A/D Channel   | 26  |

| 4 | Nep   | tune-LTI  | E Logic Interfaces                      | 28  |

|   | 4.1   | Neptune   | e LTE IC Description                    | 28  |

|   | 4.2   | Neptune   | e Functional Summary                    | 28  |

|   | 4     | .2.1 DSF  | >                                       | 28  |

|   | 4     | .2.2 ARI  | M7 MCU                                  | 28  |

|   |       | 4.2.2.1   | MCU Memory                              | 29  |

|   |       | 4.2.2.2   | MCU Peripherals                         | 29  |

|   | 4     | .2.3 Sha  | red Peripherals                         | 31  |

|   |       | 4.2.3.1   | Universal Serial Bus Module (USB)       | 31  |

|   |       | 4.2.3.2   | General Purpose I/O (GPIO)              | 31  |

|   |       | 4.2.3.3   | MCU / DSP Interface (MDI)               | 31  |

|   |       | 4.2.3.4   | Layer 1 Timer (L1T)                     | 31  |

|   | 4.3   | Neptune   | e GPIO Summary                          | 32  |

|   | 4.4   | Neptune   | e-LTE Memory Interface                  | 32  |

|   | 4     | .4.1 Flas | h                                       | 33  |

|   |       |           |                                         |     |

# E2 Level 3 Circuit Description

|   | 4.4.2 PSRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33                                                                           |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|   | 4.4.3 Neptune-LTE Chip Select Assignments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33                                                                           |

|   | 4.5 Neptune MQSPI Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 35                                                                           |

|   | 4.6 SIM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                           |

| 5 | Neptune-LTE RF Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40                                                                           |

|   | 5.1.1 RF6025 Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40                                                                           |

|   | 5.1.2 RF6025 Serial Data Interface and Device Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                           |

|   | 5.2 RF3178 (Quad-Band Power Amplifier Module) Chipset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                           |

| 6 | Application Processor (Bulverde)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                                           |

|   | 6.1 Bulverde Functional Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44                                                                           |

|   | 6.2 Bulverde Memory Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                           |

|   | 6.2.1 Bulverde SDRAM Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45                                                                           |

|   | 6.2.2 Bulverde Flash Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 47                                                                           |

|   | 6.3 Bulverde GPIO Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 48                                                                           |

|   | 6.3.1 Bulverde GPIO Operation as Application-specific GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48                                                                           |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                              |

|   | 6.3.2 Most GPIO pins are multiplexed with alternate-functions of the Bulver                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | de                                                                           |

|   | 6.3.2 Most GPIO pins are multiplexed with alternate-functions of the Bulver<br>processor. Certain modes within the serial controllers and LCD controller req                                                                                                                                                                                                                                                                                                                                                                                             |                                                                              |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                              |

|   | processor. Certain modes within the serial controllers and LCD controller req                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | uire                                                                         |

|   | processor. Certain modes within the serial controllers and LCD controller req<br>extra pins. These functions are externally available through specific GPIO                                                                                                                                                                                                                                                                                                                                                                                              | uire<br>49                                                                   |

|   | processor. Certain modes within the serial controllers and LCD controller req<br>extra pins. These functions are externally available through specific GPIO<br>pinsBulverde GPIO Operation as E2 Function                                                                                                                                                                                                                                                                                                                                                | uire<br>49<br>53                                                             |

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req extra pins. These functions are externally available through specific GPIO pinsBulverde GPIO Operation as E2 Function</li></ul>                                                                                                                                                                                                                                                                                                                                   | uire<br>49<br>53<br>53                                                       |

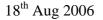

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req extra pins. These functions are externally available through specific GPIO pinsBulverde GPIO Operation as E2 Function.</li> <li>6.4 E2 Keypad Design</li></ul>                                                                                                                                                                                                                                                                                                    | uire<br>49<br>53<br>53<br>55                                                 |

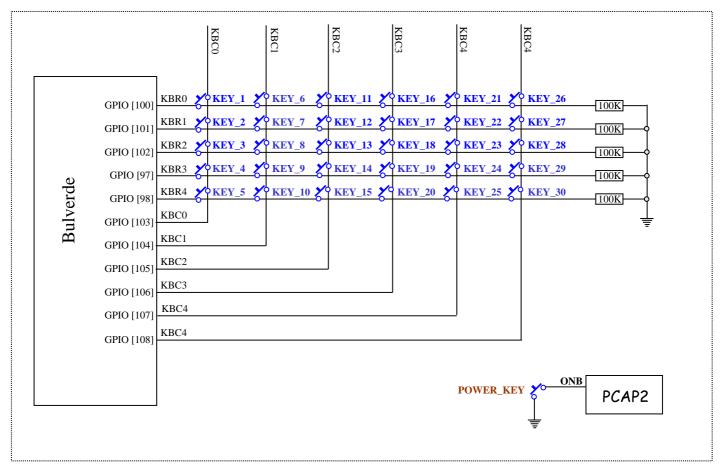

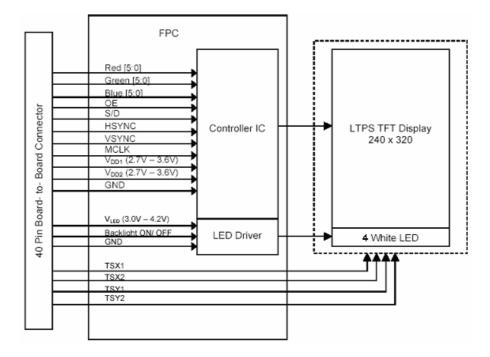

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req extra pins. These functions are externally available through specific GPIO pinsBulverde GPIO Operation as E2 Function.</li> <li>6.4 E2 Keypad Design</li></ul>                                                                                                                                                                                                                                                                                                    | uire<br>49<br>53<br>53<br>55<br>59                                           |

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req<br/>extra pins. These functions are externally available through specific GPIO<br/>pinsBulverde GPIO Operation as E2 Function</li></ul>                                                                                                                                                                                                                                                                                                                           | uire<br>49<br>53<br>53<br>55<br>59<br>60                                     |

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req<br/>extra pins. These functions are externally available through specific GPIO<br/>pinsBulverde GPIO Operation as E2 Function.</li> <li>6.4 E2 Keypad Design</li></ul>                                                                                                                                                                                                                                                                                            | uire<br>49<br>53<br>53<br>55<br>59<br>60<br>61                               |

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req<br/>extra pins. These functions are externally available through specific GPIO<br/>pinsBulverde GPIO Operation as E2 Function.</li> <li>6.4 E2 Keypad Design</li></ul>                                                                                                                                                                                                                                                                                            | uire<br>49<br>53<br>53<br>55<br>59<br>60<br>61<br>61                         |

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req extra pins. These functions are externally available through specific GPIO pinsBulverde GPIO Operation as E2 Function.</li> <li>6.4 E2 Keypad Design</li></ul>                                                                                                                                                                                                                                                                                                    | uire<br>49<br>53<br>53<br>55<br>59<br>60<br>61<br>61                         |

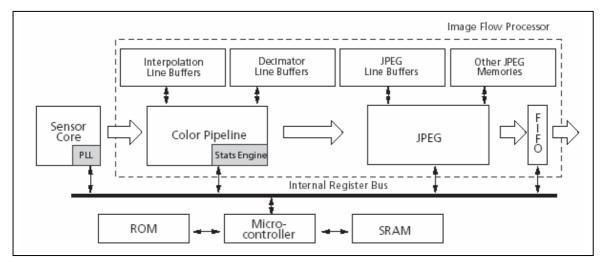

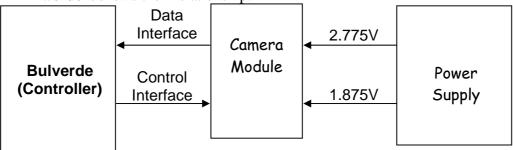

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req extra pins. These functions are externally available through specific GPIO pinsBulverde GPIO Operation as E2 Function</li> <li>6.4 E2 Keypad Design</li> <li>6.4.1 Keypad Interface</li> <li>6.5 E2 LCD Module Interface</li> <li>6.6 Bulverde Peripherals Interface</li> <li>6.6.1 Blue Tooth Module</li> <li>6.6.2 Digital Camera</li> <li>6.6.2.1 Micron<sup>TM</sup> 1.3-MegaPixel Module Features</li> <li>6.6.2.2 MT9D111 Functional Description</li> </ul> | uire<br>49<br>53<br>55<br>55<br>59<br>60<br>61<br>62<br>62                   |

|   | <ul> <li>processor. Certain modes within the serial controllers and LCD controller req extra pins. These functions are externally available through specific GPIO pinsBulverde GPIO Operation as E2 Function</li></ul>                                                                                                                                                                                                                                                                                                                                   | uire<br>49<br>53<br>53<br>55<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62 |

# E2 Level 3 Circuit Description

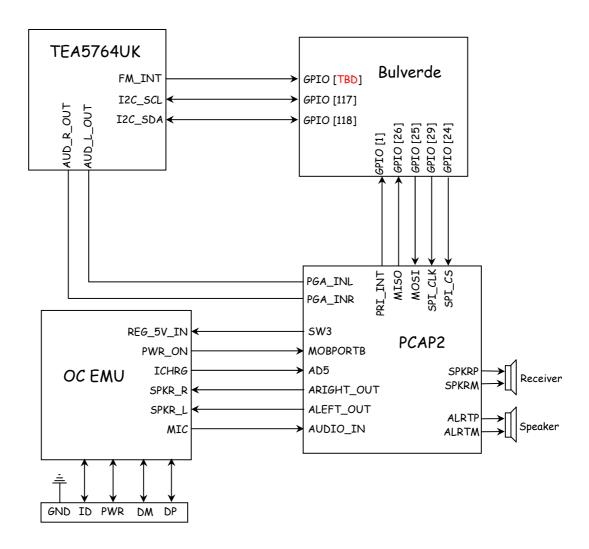

|   |       | 6.6.4.2  | FM Radio Connection Block Diagram                     | 68 |

|---|-------|----------|-------------------------------------------------------|----|

| 7 | E2 \$ | System A | Architecture Description                              | 70 |

|   | 7.1   | E2 Syst  | tem architecture block diagram                        | 70 |

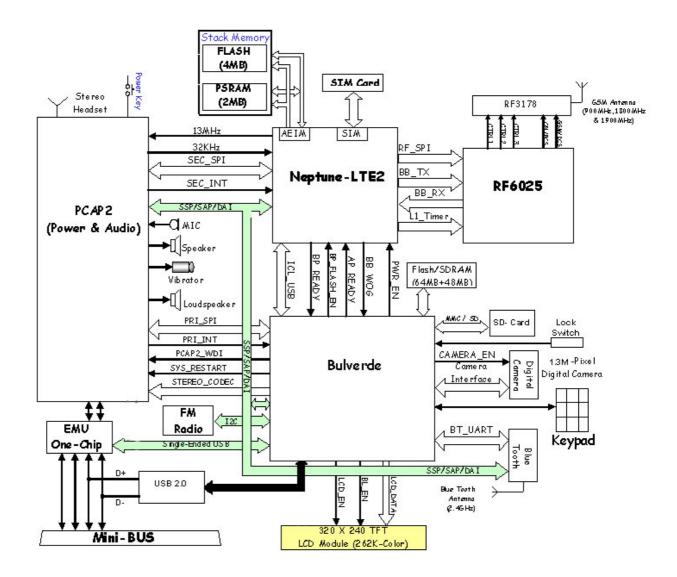

|   | 7.2   | E2 Inter | rconnection Link between Neptune-LTE & Bulverde (ICL) | 71 |

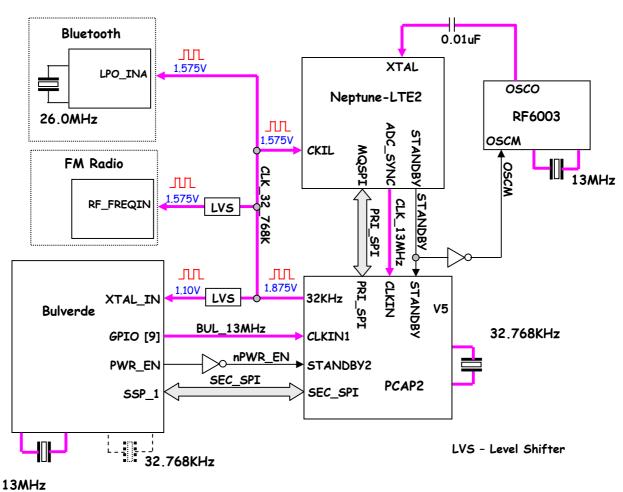

|   | 7.3   | E2 Cloc  | ck System Control                                     | 73 |

|   | 7     | .3.1 Nep | otune-LTE Related Clock Signal                        | 74 |

|   | 7     | .3.2 RFN | MD Related Clock Signal                               | 74 |

|   | 7     | .3.3 Bul | verde Related Clock Signal                            | 74 |

|   | 7     | .3.4 Blu | etooth Related Clock Signal                           | 74 |

|   | 7     | .3.5 PCA | AP2 Related Clock Signal                              | 75 |

| 8 | Bus   | and E2   | Accessories                                           | 76 |

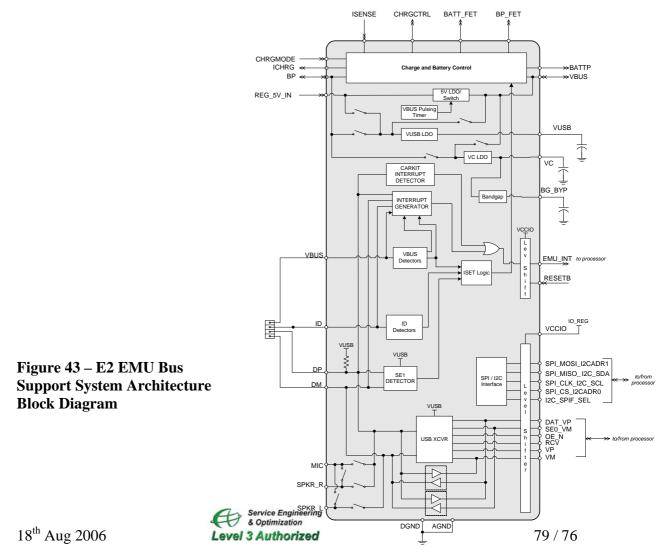

|   | 8.1   | E2 EM    | U Bus System Architecture                             | 76 |

# List of Tables:

| TABLE 1 – E2 A/D CONVERTER ALLOCATION TABLE                     |    |

|-----------------------------------------------------------------|----|

| TABLE 2- BATTERY THERMISTOR READINGS OVER TEMPERATURE           |    |

| TABLE 3 - NEPTUNE-LTE CHIP SELECT ASSIGNMENT                    |    |

| TABLE 4 - SIM CARD PRESENCE DETECT MATRIX                       | 39 |

| TABLE 5 - RF3178 ANTENNA SWITCH CONTROL TRUE TABLE              |    |

| TABLE 6 – E2 BULVERDE GPIO ASSIGNMENT (GPIO [0] ~ GPIO [34])    |    |

| TABLE 7 – E2 BULVERDE GPIO ASSIGNMENT (GPIO [35] ~ GPIO [69     | 50 |

| TABLE 8 – E2 BULVERDE GPIO ASSIGNMENT (GPIO [70] ~ GPIO [104])  | 51 |

| TABLE 9 – E2 BULVERDE GPIO ASSIGNMENT (GPIO [105] ~ GPIO [120]) |    |

| TABLE 10 – E2 MATRIX SCAN KEY ASSIGNMENT                        | 53 |

| TABLE 11 – E2 BULVERDE GPIO ASSIGNMENT OF KEYPAD CONTROLLER     |    |

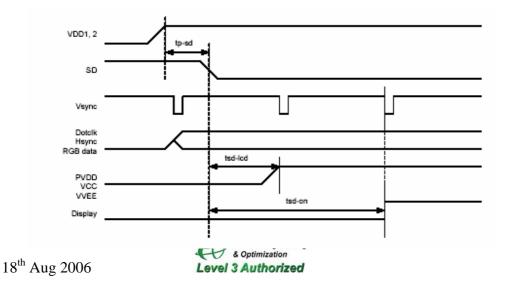

| TABLE 12 – AE2 LCD POWER UP TIMING FIGURES                      | 57 |

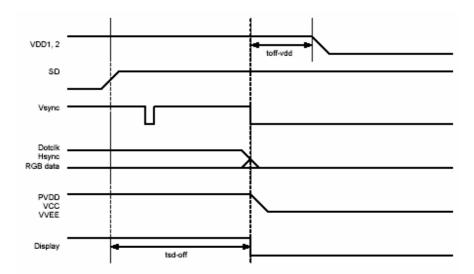

| TABLE 13 – E2 LCD POWER DOWN TIMING FIGURES                     | 57 |

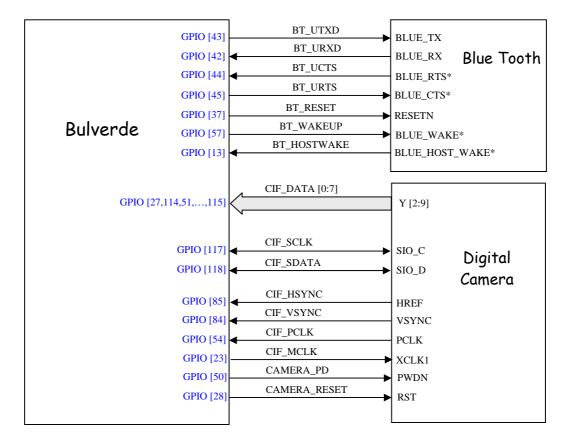

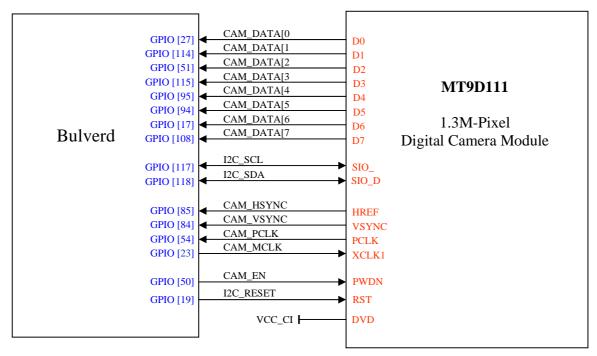

| TABLE 14 – E2 DIGITAL CAMERA SIGNAL FUNCTION DESCRIPTION        | 63 |

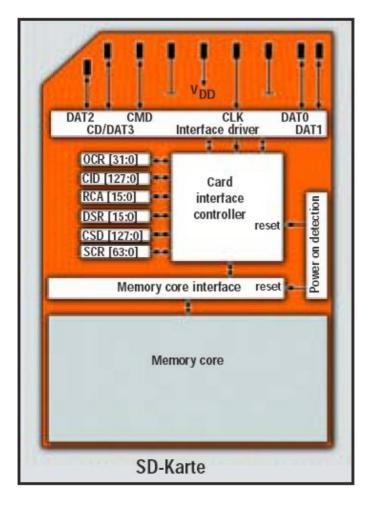

| TABLE 15 - SD-FLASH CARD PIN DEFINITION                         | 65 |

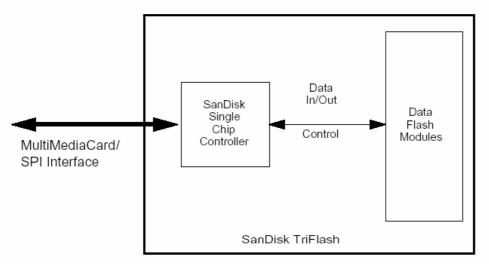

| TABLE 16 - TRI-FLASH CARD MMC BUS AND SPI BUS COMPARISON        | 65 |

| TABLE 17 – E2 ICL SIGNALS FUNCTION DESCRIPTION                  |    |

# List of Figures:

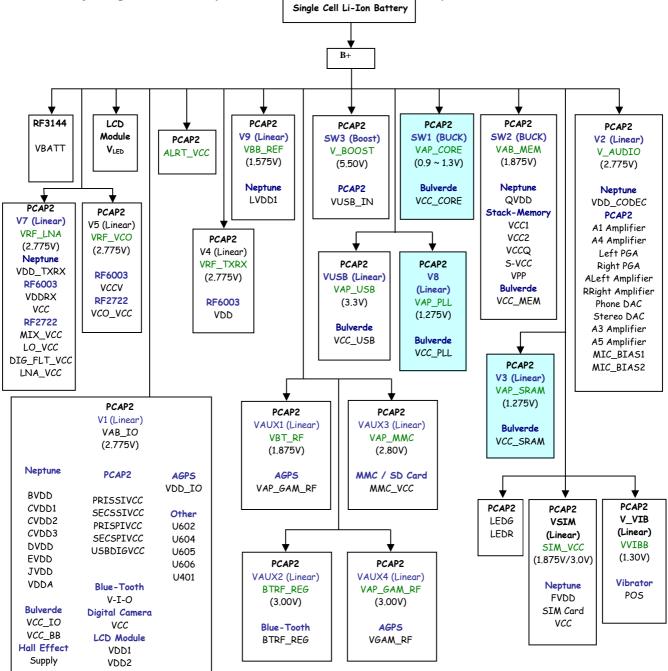

| FIGURE 1 - POWER DISTRIBUTION TREE.                                       | 13   |

|---------------------------------------------------------------------------|------|

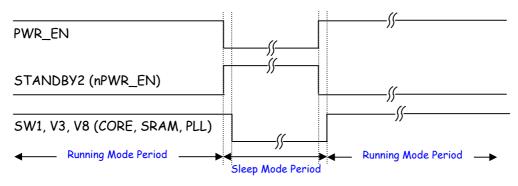

| FIGURE 2 – E2 BULVERDE SLEEP AND OPERATION MODE POWER SUPPLY CONTROL      | 14   |

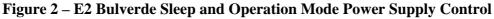

| FIGURE 3 – E2 AUDIO ROUTING AND SPI CONTROL BLOCK DIAGRAM                 | 15   |

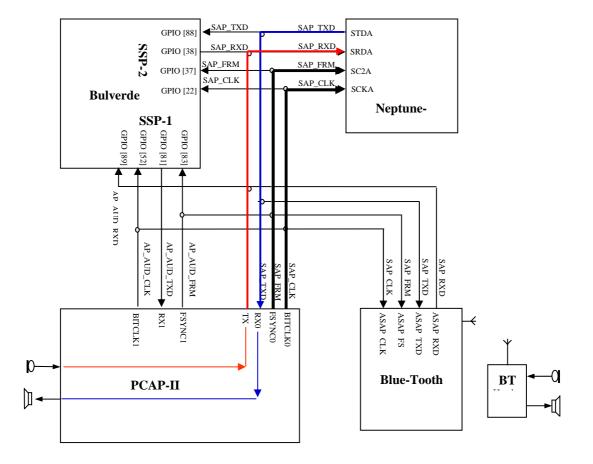

| FIGURE 4 – E2 AUDIO SYSTEM ARCHITECTURE BLOCK DIAGRAM – SAP COMMUNICATION | ON - |

| DURING VOICE CALL                                                         | 16   |

| FIGURE 5 – E2 AUDIO SYSTEM ARCHITECTURE BLOCK DIAGRAM – SAP COMMUNICATION | ON - |

| DURING BLUE-TOOTH VOICE CALL                                              | 17   |

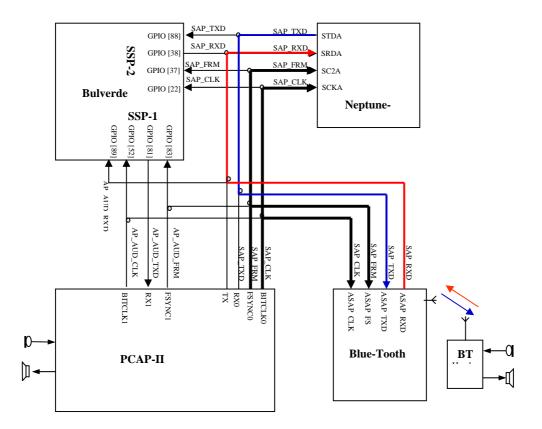

| FIGURE 6 – E2 AUDIO SYSTEM ARCHITECTURE BLOCK DIAGRAM – SAP COMMUNICATION | ON   |

| –VOICE RECORD DURING CALL                                                 | . 18 |

| FIGURE 7 – E2 AUDIO SYSTEM ARCHITECTURE BLOCK DIAGRAM – SAP COMMUNICATION | ON   |

| –VOICE RECORD DURING BLUE-TOOTH CALL                                      | 19   |

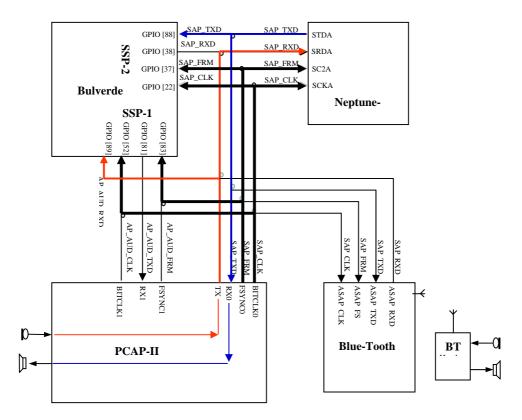

| FIGURE 8 – E2 AUDIO SYSTEM ARCHITECTURE BLOCK DIAGRAM – SAP COMMUNICATION | ON   |

| –Local Audio Record                                                       |      |

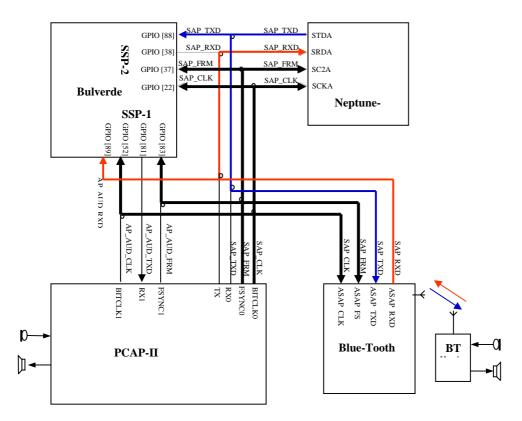

| FIGURE 9 – E2 AUDIO SYSTEM ARCHITECTURE BLOCK DIAGRAM – SAP COMMUNICATIO  | DN – |

| LOCAL AUDIO PLAYBACK (MP3, FM RECEIVER, VOICE NOTES, SOUNDS)              | 21   |

| FIGURE 10 - PCAP AUDIO INPUT SECTION                                      | 22   |

| FIGURE 11 - PCAP2 AUDIO OUTPUT SECTION BLOCK DIAGRAM                      | 23   |

| FIGURE 12 - PCAP2 A/D CONVERSION TIMING DIAGRAM WITH AD_SEL = 0           | 24   |

| FIGURE 13 - PCAP2 A/D CONVERSION TIMING DIAGRAM WITH AD_SEL = 1           | 24   |

| FIGURE 14 - BATTERY THERMISTOR CONNECTION BLOCK DIAGRAM                   | 26   |

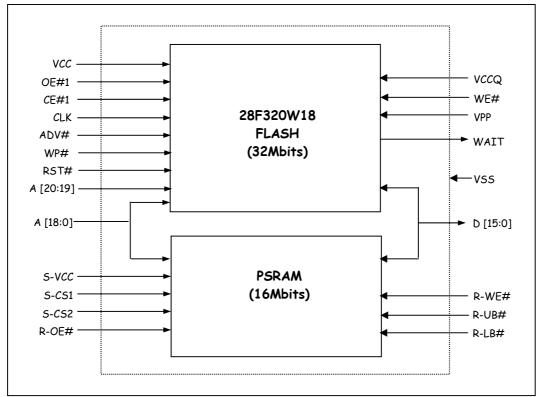

| FIGURE 15 - E2 BASEBAND 32W18 + 16MB SRAM STACKED-CSP BLOCK DIAGRAM       | 32   |

| FIGURE 16 – E2 BASEBAND NEPTUNE-LTE AND MEMORY CONNECTION BLOCK DIAGRA    | ٩M   |

|                                                                           | 34   |

| FIGURE 17 - NEPTUNE MQSPI CONNECTION WITH PCAP2 AND RF6025 BLOCK DIAGRA   | AM   |

|                                                                           | 36   |

| FIGURE 18 – E2 SIM CONNECTION BLOCK DIAGRAM                               | 37   |

| FIGURE 19 – E2 SIM PRESENT DETECTION CIRCUIT LOGIC BLOCK DIAGRAM          | 38   |

| FIGURE 20 - RF6025 FUNCTIONAL BLOCK DIAGRAM                               | 41   |

| FIGURE 21 - RF3178 FUNCTIONAL BLOCK DIAGRAM                               | 42   |

| FIGURE 22 - BULVERDE MEMORY CONNECTION BLOCK DIAGRAM                      | 45   |

| FIGURE 24 – E2 KEYPAD INTERFACE BLOCK DIAGRAM                             | 53   |

| FIGURE 25 – E2 LCD MODULE ELECTRICAL BLOCK DIAGRAM                        | 55   |

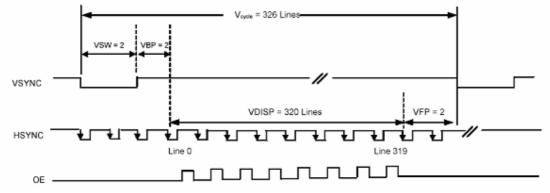

| FIGURE 26 – E2 LCD MODULE HORIZONTAL READING / WRITING TIMING DIAGRAM     | 56   |

| FIGURE 27 – E2 LCD MODULE VERTICAL READING / WRITING TIMING DIAGRAM       | 56   |

| FIGURE 28 – E2 LCD POWER UP TIMING DIAGRAM                                | 56   |

| FIGURE 29 – E2 LCD POWER DOWN TIMING DIAGRAM                              | 57   |

| FIGURE 30 – E2 CONNECTION BLOCK DIAGRAM BETWEEN BULVERDE AND LCD MO | DULE |

|---------------------------------------------------------------------|------|

|                                                                     | 58   |

| FIGURE 31 – E2 BULVERDE PERIPHERALS CONNECTIONS BLOCK DIAGRAM       | 59   |

| FIGURE 32 - BCM2045 FUNCTIONAL BLOCK DIAGRAM                        | 60   |

| FIGURE 33 - MT9D111 FUNCTIONAL BLOCK DIAGRAM                        | 62   |

| FIGURE 34 – E2 DIGITAL CAMERA SYSTEM ARCHITECTURE BLOCK DIAGRAM     | 62   |

| FIGURE 35 – E2 DIGITAL CAMERA DETAILED CONNECTION WITH BULVERDE     | 63   |

| FIGURE 36 - SD-FLASH CARD OUTLINE DIAGRAM                           | 65   |

| FIGURE 37 - SD-FLASH WITH MMC AND SPI INTERFACE BLOCK DIAGRAM       | 65   |

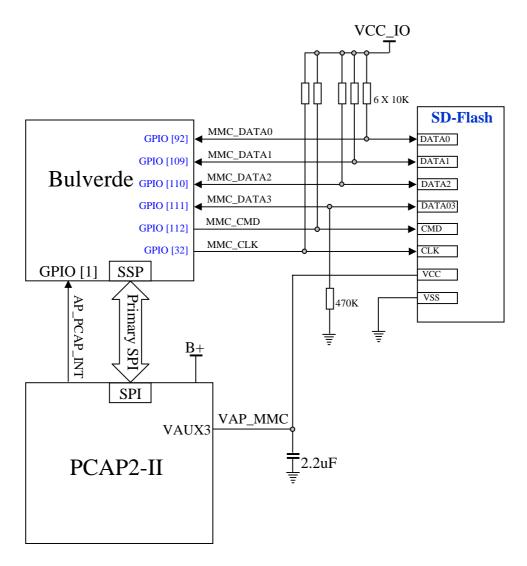

| FIGURE 38 – E2 SD-FLASH CARD CONTROL BLOCK DIAGRAM                  | 66   |

| FIGURE 39 – E2 FM RADIO AND AUDIO RELATED SIGNAL BLOCK DIAGRAM      | 68   |

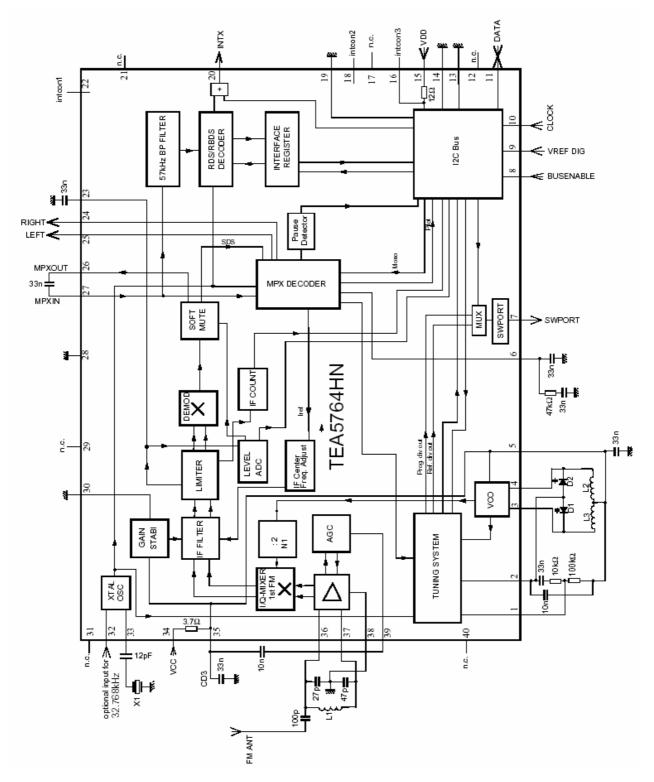

| FIGURE 40 - PHILLIPS TEA5764 FUNCTION BLOCK DIAGRAM                 | 69   |

| FIGURE 41 – E2 QUAD-BAND SYSTEM ARCHITECTURE BLOCK DIAGRAM          | 70   |

| FIGURE 42 – E2 INTERCONNECTION LINK BETWEEN NEPTUNE, BULVERDE & EMU | 72   |

| FIGURE 43 – E2 CLOCK SYSTEM CONTROL BLOCK DIAGRAM                   | 73   |

| FIGURE 44 – E2 EMU BUS                                              |      |

|                                                                     |      |

# 1 Revision History

| Revision Date |                           | Section | Author |  |

|---------------|---------------------------|---------|--------|--|

| 1.0           | 22 <sup>th</sup> Dec 2005 | STD     | STD    |  |

# 2 Introduction and Purpose

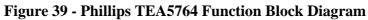

The purpose of this document is to list and define the hardware system interfaces for E2 cellular phone. This phone is based out of EZX platform which consisting Neptune-LTE2 IC (base band call processor), Bulverde IC (adjunct application processor), PCAP2 (Platform Audio Interface and Power Control) IC, EMU Bus One-Chip IC, as well as the RFMD chips such as RF6025 IC and RF3178 power amplifier IC.

In this document, the major chipset features and functionality will be introduced as well as the dedicated usage in E2 phone design. The interconnections between Neptune-LTE2 and Bulverde will be introduced in detail. The control signals from Neptune-LTE2 to RF6025 and RF3178 will also be introduced.

# **3 PCAP2 Hardware Overview**

This section describes the general features of the PCAP2 (Platform Control/Audio/Power) IC. The PCAP2 architecture is derived from previous devices such as GCAP-III and GCAP1, with feature enhancements as needed to support requirements of next-generation mobile terminals.

The system-level requirements that have created the need for a new PCAP2 device include the following:

- Improved Power Cut/Power Power supply and control for external

- Stereo Audio capability for Multimedia support

- Dedicated Transceiver power supply

- The PCAP2 will also include additional features to improve system efficiency and reduce external component count such as:

- Dual SPI control interface to allow access from two independent base band processors

- Multiple Switch mode power supply controllers for buck and/or boost conversion

- Additional independent, configurable voltage regulators

- Enhanced touch screen interface

- Improved backlight controller capability

Certain functions that were available on previous devices such as GCAP-II, GCAP-III will NOT be carried over to the PCAP2 parts due to changes in system requirements or lack of use on previous products.

These include:

- Internal over voltage protection / clamp as implemented in CCAP

- Negative voltage generation charge pump

- Negative voltage linear regulators

- DSC serial communication interface

# **3.1 Power Management**

#### 3.1.1 Regulator Usage Description

Regulators of PCAP2 were assigned as dedicated power supplies for Neptune-LTE or Bulverde side. The functions were listed as below.

1) V1 Linear Regulator

For E2, V1 is programmed to 2.775V and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 2.775V as default. V1 supplies Neptune-LTE2 analog modules and RF6025 SPI port. V1 is also used to provide I/O voltages to Bulverde sub-system. Some external level shifters power supplies were also provided by V1. V1 was assigned as label AP\_IO\_REG in E2 schematic.

#### 2) V2 Linear Regulator

For E2, V2 is programmed to 2.775V and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 2.775V as default. V2 supplies Neptune internal CODEC circuitry power supply and PCAP2 internal audio related circuitry such as audio amplifiers, microphone bias etc. V2 was assigned as label AUD\_REG in E2 schematic.

3) V3 Linear Regulator

For E2, V3 is programmed to 1.275V and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 1.275V as default. V3 supplies the power for Bulverde VCC\_SRAM power. V3 was assigned as label VCC\_SRAM in E2 schematic. This regulator can be switched off when Bulverde entering into sleep mode, the control signal for this is PWR\_EN of Bulverde.

4) V4 Linear Regulator

For E2, V4 is programmed to 2.775V as default. V4 supplies the power for PCAP2 internal circuitry such as SPI module and Neptune-LTE2 IO supply. V4 was assigned as BB\_IO\_REG in E2 schematic.

#### 5) V5 Linear Regulator

For E2, V5 is programmed to 2.775V as default. V5 supplies the power for PCAP2 internal circuitry such as SPI module and RF2025 related circuitry etc. V5 was assigned as VCO\_REG in E2 schematic.

#### 6) V6 Linear Regulator

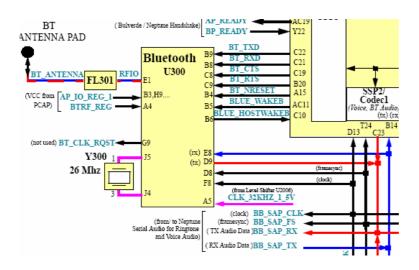

For E2, V6 is used as Bluetooth RF power supply.

#### 7) V7 Linear Regulator

For E2, V7 is programmed to 2.775V and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 2.775V as default. V7 supplies to RF6025 related circuitries. V7 was assigned as label RF\_REG in E2 schematic.

8) V8 Linear Regulator

For E2, V8 is programmed to 1.275V and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 1.275V as default. V8 supplies the power for Bulverde VCC\_PLL power. V8 was assigned as label VAP\_PLL in E2 schematic. This regulator can be switched off when Bulverde entering into sleep mode, the control signal for this is PWR\_EN of Bulverde.

9) V9 Linear Regulator

For E2, V9 is programmed to 1.575V and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 1.575V as default. V9 supplies to Neptune LVDD1 as Neptune internal reference voltage. V9 was assigned as label REF\_REG in E2 schematic.

10) V10 Linear Regulator

.V10 is not used in E2 design.

11) VAUX1 Linear Regulator

VAUX1 is not used in E2.

12) VAUX3 Linear Regulator

For E2, VAUX3 is programmed to 2.800V and is supplied directly by B+. This regulator is off when the radio is turned on, and the initial power-up level is 0V as default. VAUX3 supplies power to Trans-Flash card. VAUX3 was assigned as label VCC\_TRANSFLASH in E2 schematic.

13) VAUX4 Linear Regulator

VAUX4 is not used in E2.

18<sup>th</sup> Aug 2006

# 14) SW1 Switching Regulator

For E2, SW1 is programmed to 1.2V and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 1.20V as default. SW1 supplies power to Bulverde VCC\_CORE domain. SW1 was assigned as label AP\_CORE in E2 schematic.

#### 15) SW2 Switching Regulator

For E2, SW2 is programmed to 1.875V and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 1.875V as default. SW2 supplies power to Bulverde memory system and Neptune-LTE2 memory interface. SW2 was assigned as label VBUCK in E2 schematic.

#### 16) SW3 Switching Regulator

For E2, SW3 is programmed to 5.5V as default and is supplied directly by B+. This regulator is on whenever the radio is turned on, and the initial power-up level is 5.50V as default. SW3 supplies power to EMU Bus One-Chip and Fun-Light LEDs. SW3 was assigned as label VBOOST\_EMU in E2 schematic.

# 3.1.2 Power Distribution Tree

PCAP2 provides all the regulated power supplies to Neptune-LTE subsystem, Bulverde adjunct processor sub-system, Bluetooth system and other system etc.

**Figure 1 - Power Distribution Tree**

18<sup>th</sup> Aug 2006

# 3.1.3 E2 Power Management Control

There are two standby control signals in PCAP2, which is different from PCAP design. In E2 power management design, one standby control pin of PCAP2 is connected to Neptune-LTE standby pin and another standby control pin is connected to Bulverde PWR\_EN pin. (It needs to be inverted as PCAP2 required).

During the period of Neptune-LTE in standby mode, Neptune-LTE asserts its STANDBY pin and PCAP2 shutdown the power supplies to Neptune-LTE subsystem needed to be for power saving purpose. The power supplies need to be switched off for Neptune-LTE standby mode are V7, V4 & V5.

In E2 adjunct processor power saving mode, Bulverde needs to enter into Sleep mode for achieving minimum power consumption. That needs the power supplies provided to Bulverde Core, PLL and internal SRAM power domain to be switched off after Bulverde entered into sleep mode. The pin PWR\_EN of Bulverde will be changed from logic HIGH to logic LOW after Bulverde entering into Sleep mode. The inverted PWR\_EN (nPWR\_EN) was connected with PCAP2 STANDBY2 pin in E2, so when STANDBY2 of PCAP2 was changed from logic LOW to logic HIGH, the power supplies to Bulverde Core, PLL and internal SRAM can be shutdown. Two types of power supplies involved into Bulverde sleep mode operation, one is a linear regulator and another one is switching mode regulator.

**Fehler! Verweisquelle konnte nicht gefunden werden.** illustrates the waveform of control sequence for VCC\_SRAM, VCC\_PLL, and VCC\_CORE with PWR\_EN.

The state of PWR\_EN signal of Bulverde will change from high to low automatically after software entering into sleep mode and can automatically change back to high from low while triggered by wakeup events settled by software. There is a small delay for SW1, V3 and V8 to setup after STANDBY2 pin changed from high to low. But that is within the timing requirement of Bulverde.

# 3.1.4 E2 Audio Routing and SPI Control

The audio system of E2 composed of Neptune, Bulverde and PCAP2. Neptune and Bulverde control the PCAP2 audio portion through the SPI port. E2 audio routing and SPI control connection block diagram shows in **Fehler! Verweisquelle konnte nicht gefunden werden**.

Figure 3 – E2 Audio Routing and SPI Control Block Diagram

# 3.2 E2 Audio System and PCAP2 Audio Section

#### 3.2.1 E2 Audio System Architecture Block Diagram

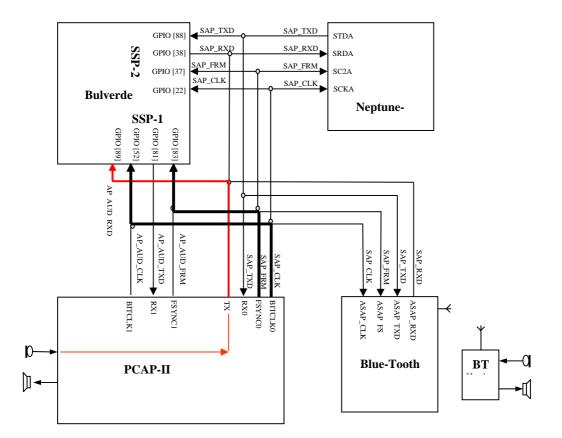

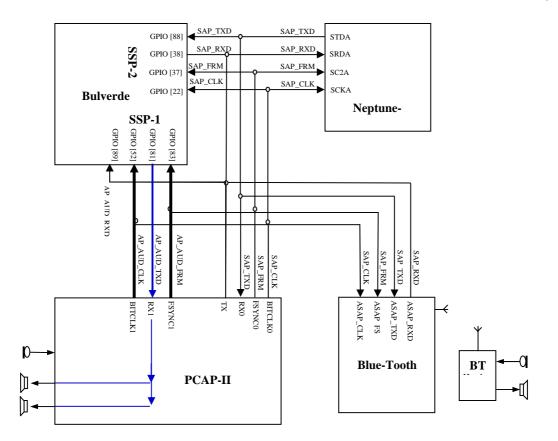

AE2 phone design supports the voice audio, stereo audio and Bluetooth audio as shown in **Fehler! Verweisquelle konnte nicht gefunden werden.**<u>-10</u>. The RX path is shown in Blue, the TX path is shown in Red. Clock and Frame Synchronisation are highlighted in thick black lines.

# **During Voice Call**

Figure 4 – E2 Audio System Architecture Block Diagram – SAP communication during Voice Call-

**During Blue-Tooth Voice Call**

Figure 5 – E2 Audio System Architecture Block Diagram – SAP communication during Blue-Tooth Voice Call-

# Voice Record During Call

Figure 6 – E2 Audio System Architecture Block Diagram – SAP communication – Voice Record During Call-

Service Engineering

& Optimization

18<sup>th</sup> Aug 2006

Voice Record During Blue-Tooth Call

Figure 7 – E2 Audio System Architecture Block Diagram – SAP communication – Voice Record During Blue-Tooth Call-

Local Audio Record

Figure 8 – E2 Audio System Architecture Block Diagram – SAP communication – Local Audio Record-

Local Audio Playback

Figure 9 – E2 Audio System Architecture Block Diagram –SAP communication – Local Audio Playback (MP3, FM Receiver, Voice Notes, Sounds)-

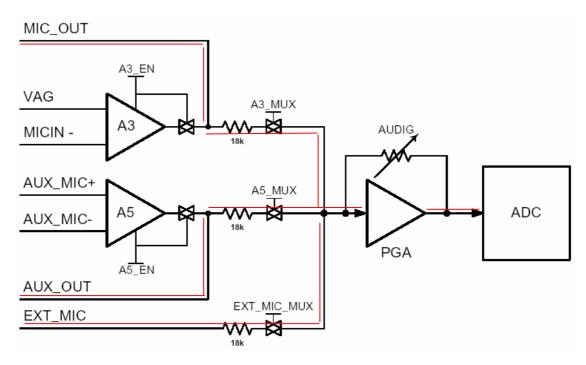

#### 3.2.2 Audio Input Section

PCAP2 Audio Input Section block diagram shows in <u>Figure11</u>. Any one of three equivalent microphone inputs can be selected. These inputs are MIC\_OUT (HJACK\_MIC), AUX\_OUT (INT\_MICP) and EXT\_MIC (AUDIO\_IN). These three inputs are single ended. The differential input microphone amplifier A3 and A5 are not in use.

Figure 10 - PCAP Audio Input Section

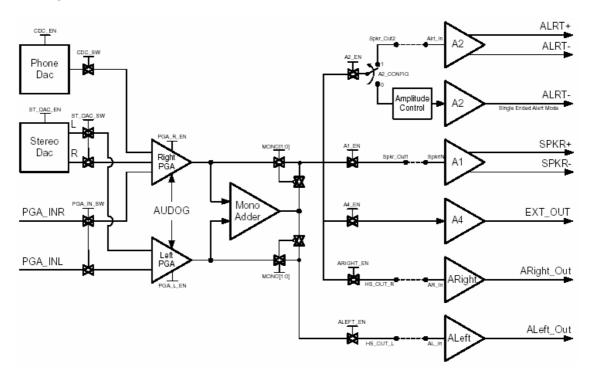

#### 3.2.3 Audio Output Section

PCAP2 Audio Output section block diagram shows in **Fehler! Verweisquelle konnte** nicht gefunden werden.

Figure 11 - PCAP2 Audio Output Section Block Diagram

It shows that the audio out of the telephone CODEC or the right channel of the stereo DAC can be routed via the right PGA to any one of four outputs. These outputs are: the internal earpiece speaker amplifier, A1, the alert amplifier, A2, the external speaker amplifier, A4, or the dedicated headset right channel speaker amplifier, ARight. The Mono adder can be used to sum the left and right channels of the stereo DAC or signals supplied to the left and right PGA inputs. The Mono adder can then attenuate the summed signals by 0dB, 3dB or 6dB and an identical monophonic signal to any of output amplifiers mentioned above.

#### 3.3 A/D Conversion And Channel Allocations

The A/D conversion functions are performed by PCAP2 chipset through the connections between PCAP2 and Neptune-LTE, PCAP2 and Bulverde via read & write accessing SPI port. The A/D converter of PCAP2 is a 14-Channel, 10-bit converter with a state machine to control the various modes of operation. That 14-channel input is split into two groups and each one with 7-channel.

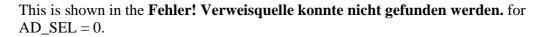

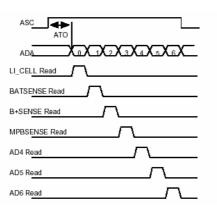

AD\_SEL (internal signal) selects between two groups of 7 input signals. If set to Zero then LiCell, BATSENSE, B+SENSE, MPBSENSE, AD4, AD5, and AD6 are read and stored into the PCAP2 registers when the conversion finished. If AD\_SEL is set to One then AD7, AD8, AD9, TSX1, TSX2, TSY1, and TSY2 are read and stored. This is done to shorten the total read time and to reduce the required storage of converted values.

Figure 12 - PCAP2 A/D Conversion Timing Diagram with AD\_SEL = 0

If AD\_SEL = 1 then the channels converted are as shown in **Fehler! Verweisquelle konnte nicht gefunden werden.**

18<sup>th</sup> Aug 2006

#### 3.3.1.1.1.1 Figure 13 - PCAP2 A/D Conversion Timing Diagram with AD\_SEL = 1

E2 A/D converter allocation listed in **Fehler! Verweisquelle konnte nicht gefunden** werden.

|       |                        | Address    |                                                                                                               |                     |                |

|-------|------------------------|------------|---------------------------------------------------------------------------------------------------------------|---------------------|----------------|

| Input | Internal /<br>External | Signal     | Purpose                                                                                                       | Condition           | A/D<br>Voltage |

| AD1   | Internal               | Li-Cell    | Backup cell voltage monitoring                                                                                | 1.5V ~ 4.5V         | 0.4V ~ 2.3V    |

| AD2   | Internal               | BATT_SENSE | Battery terminal voltage monitor<br>for charge & discharge control                                            | 2.0V ~ 5.5V         | 0.4V ~ 2.3V    |

| AD3   | Internal               | B+_SENSE   | B+ terminal voltage monitor for<br>charge & discharge control                                                 | 2.5V ~ 6.5V         | 0.4V ~ 2.3V    |

| AD4   | Internal               | MPBSENSE   | EXT_B_ terminal voltage<br>monitor for charger type<br>identification and charge control                      | 2.7V ~ 6.5V         | 0.4V ~ 2.3V    |

| AD5   | External               | BATT_THERM | Connect with battery thermo<br>voltage for battery pack<br>temperature monitor during<br>charge and discharge | 25°C                | 1.28V          |

| AD7   | External               | /          | Not used in E2 design                                                                                         | N/A                 |                |

| AD6   | External               |            | Connect with Mini-USB                                                                                         | Mid-Rate            | 1.254V         |

| AD6   | External               | CHRG_ID    | connector and functions as<br>accessory ID identify                                                           | Full-Rate           | 1.955V         |

| AD9   | External               | /          | Not used in E2 design                                                                                         | N/A                 | N/A            |

| AD8   | External               | /          | Not used in E2 design                                                                                         | N/A                 | N/A            |

| AD10  | External               | /          | Not used in E2 design                                                                                         | N/A                 | N/A            |

| AD11  | External               | TSX1       | Connect with resistive touch<br>panel for X - position reading                                                | Position dependence | 0.4V ~ 2.3V    |

| AD12  | External               | TSX2       | Connect with resistive touch<br>panel for X - position reading                                                | Position dependence | 0.4V ~ 2.3V    |

| AD13  | External               | TSY1       | Connect with resistive touch<br>panel for Y - position reading                                                | Position dependence | 0.4V ~ 2.3V    |

| AD14  | External               | TSY2       | Connect with resistive touch panel for Y - position reading                                                   | Position dependence | 0.4V ~ 2.3V    |

Table 1 – E2 A/D Converter Allocation Table

Service Engineering & Optimization

Level 3 Authorized

#### 3.3.2 Detailed Description Of Each A/D Channel

#### 1) (AD1 internal PCap) (LICELL)

The coin cell battery voltage can be monitored at this channel of A/D converter. This can be used to do the decision for power cut, user off etc functions.

#### 2) (AD2) (BATTI)

This A/D converter input directly is connected with battery positive pin for terminal voltage monitoring for both charge & discharge battery gas-gauge display. This A/D input comes from PCAP2 pin **BATTI** with which battery positive pin internally connected.

#### 3) (AD3) (PCAP\_BP)

This A/D converter input is connected with B+ and is used to do the voltage monitoring during discharge. Software can use this A/D channel to do the software shutdown when the battery voltage is too low to provide the power to the whole phone. The threshold of shutdown is stored in the battery EPROM and was read back during the phone power up.

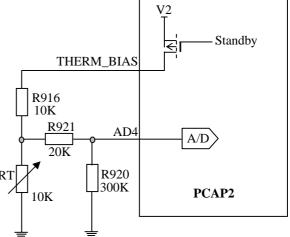

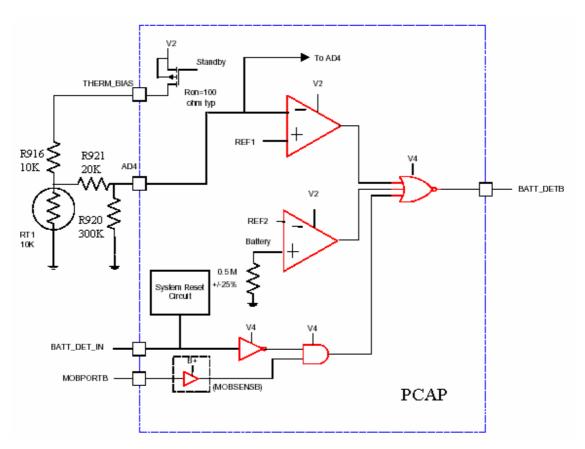

#### 5) (AD4) (THERM)

This A/D channel is used to do the monitoring of battery pack temperature. There is a thermo-resistor built into the battery pack, which can be used to do the temperature measurement for battery charge and discharge safety use purpose. This A/D channel is internally connected with AD4 of PCAP2 with which battery pack thermo-resistor connected. The connection block diagram shown in **Fehler! Verweisquelle konnte nicht gefunden werden.**.During standby mode operation period, the Standby signal will disconnect the V2 from the thermo-resistor for power saving. The voltage input to AD4 should be within 0.4V ~ 2.3V.

The characteristic of the thermo-resistor is in **Fehler! Verweisquelle konnte nicht gefunden werden.**.

There is a capacitor connected at AD5 with ground for interference proof.

At room temperature, the nominal resistance of RT is  $10K\Omega$ . And the voltage at AD5 is 1.28V. When the battery pack is removed from the board, the voltage at AD4 is 2.70V roughly.

18<sup>th</sup> Aug 2006

26/76

| Temperature | <b>R</b> <sub>Thermistor</sub> | Voltage |  |

|-------------|--------------------------------|---------|--|

| °C          | KΩ                             | V       |  |

| No Battery  | Infinity                       | 2.52    |  |

| -40         | 336.60                         | 2.45    |  |

| -35         | 242.80                         | 2.43    |  |

| -30         | 177.00                         | 2.39    |  |

| -25         | 130.40                         | 2.35    |  |

| -20         | 97.12                          | 2.29    |  |

| -15         | 92.98                          | 2.28    |  |

| -10         | 55.34                          | 2.15    |  |

| -5          | 42.34                          | 2.05    |  |

| 0           | 32.66                          | 1.95    |  |

| 5           | 25.40                          | 1.83    |  |

| 10          | 19.90                          | 1.7     |  |

| 15          | 15.71                          | 1.56    |  |

| 20          | 12.49                          | 1.42    |  |

| 25          | 10.00                          | 1.28    |  |

| 30          | 8.06                           | 1.15    |  |

| 35          | 6.53                           | 1.02    |  |

| 40          | 5.33                           | 0.89    |  |

| 45          | 4.37                           | 0.78    |  |

| 50          | 3.60                           | 0.68    |  |

| 55          | 2.99                           | 0.59    |  |

| 60          | 2.49                           | 0.52    |  |

| 65          | 2.08                           | 0.45    |  |

| 70          | 1.75                           | 0.39    |  |

| 75          | 1.48                           | 0.33    |  |

| 80          | 1.26                           | 0.29    |  |

Figure 14 - Battery Thermistor Connection Block Diagram

# Table 2- Battery Thermistor Readings Over Temperature

#### 5) (AD5) (ACC\_ID)

This channel A/D connected internally with EXT\_B+. This A/D can be used to monitor the charger's /accessory type prior to charging.

# 4 Neptune-LTE Logic Interfaces

E2 Quad-band design decided to use Neptune-LTE 257-PIN as its base band call processor chipset IC. Neptune-LTE IC is a digital base band processor for the 2.5 / 2.75G GSM market. It is a dual-core processor that contains a Synthesizable Onyx DSP core (566xx), an ARM7TDMI-S micro-controller, and custom peripherals.

Neptune-LTE is available in two packages; 257-Pin Neptune-LTE chipset is used in E2 Quad-band final design.

Neptune-LTE connects with Bulverde, PCAP2, RF6025 etc to build the E2 system architecture.

#### 4.1 Neptune LTE IC Description

The Neptune IC is a digital baseband processor. It is a dual-core processor that contains a Synthesizable Onyx DSP core (566xx), an ARM7TDMI-S micro controller, and custom peripherals. The Neptune IC is optimized for 2.5G GSM based applications. The Neptune IC will be ROM-based using mainly internal memory and an external flash. The Neptune IC is optimized for GSM based applications.

#### **4.2 Neptune Functional Summary**

#### 4.2.1 DSP

The DSP56600 S-ONYXU core in Neptune operates at a maximum output frequency of 104 MHz. This performance will be utilized to support General Packet Radio Service (GPRS), High Speed Circuit Switched Data (HSCSD), extended Voice Annotation (VA), Voice Recognition (VR), and other features.

#### 4.2.2 ARM7 MCU

The ARM7TDMI-S is a member of the ARM family of general-purpose 32-bit microprocessors. The ARM family offers high performance for very low power consumption and gate count.

The ARM7 MCU core in Neptune operates at a frequency up to 52 MHz. The increase in processor frequency will increase performance of critical routines located in internal memory.

# 4.2.2.1 MCU Memory

Neptune has 901K x32 of internal memory accessible by the MCU. A 792Kx32 block of internal memory will be implemented as ROM, while the remaining 109Kx32 block will be implemented as RAM.

# 4.2.2.2 MCU Peripherals

The functions of the MCU peripherals for the Neptune IC are summarized below. Each peripheral provides the ability to disable the clock at the input to the module. Each peripheral provides a software reset capability. The software reset must reset the peripheral in the same way as a system reset. Neptune includes some clock control logic outside of the peripheral blocks. The Clock Control Module handles this supplemental clock control.

# 1) Multiple Queue Serial Peripheral Interface (MQSPI)

The MQSPI provides two (2) independent QSPI channels which performs the serial programming operations to configure the RF subsystem and selected peripherals. It is designed to minimize the amount of MCU interaction by automating multiple and repetitive serial data transfers. The module has multiple queues to hold these transfers. Module transfers can be triggered by the Layer 1 Timer.

#### 2) SIM Interface Modifications (SIM)

The SIM module is a customized UART with additional features allowing for communication with SmartCards and conforming to the ISO 7816 specification.

#### 2) Universal Asynchronous Receiver Transmitter (UART)

A UART module performs all normal operations associated with "start-stop" asynchronous communications. The UART transmit and receive buffer sizes are 32 bytes each. The UART modules will operate at 115.2Kbps, 460Kbps, and 920Kbps based on a 13MHz input reference clock.

#### 3) Deep Sleep Module (DSM)

The Deep Sleep Module allows for optimal power savings in idle modes by allowing the Neptune IC to synchronize to the frame timing automatically even though the timing reference has been removed from the part during the idle time.

#### 4) Watchdog Timer (WDOG)

The Watchdog Timer is used to protect against system failures by providing a means to escape from unexpected events or application errors. Once started, the timer must be serviced by the core on a periodic basis. If servicing does not occur, the module time out and asserts the reset signal.

#### 5) Keypad Port (KPP)

The Keypad port is a module that is used for keypad matrix scanning.

#### 6) Real Time Clock (RTC)

The real time clock (RTC) module consists of counters and registers used to maintain the day, time of day and alarm values. The RTC operates even when the phone is powered down and the alarm function can turn it on and alert the processor. If the phone is already on, the processor is interrupted. The RTC uses a frequency reference generated on the PCAP2 using a low-cost crystal and inaccuracies in the frequency may be compensated for by trimming the modulus register value. The RTC module also provides power cut logic, and keep-alive memory that activates when a low battery condition is detected.

#### 20) Display Memory Access Controller (DMAC)

The DMAC (display memory access controller) module is designed to transfer data from the display frame buffer in system memory to an external LCD display device.

#### 21) Clock Control Module (CCM)

The Clock Control Module handles all intermodule clock routing, the selection of multiple input clock sources for the cores and various peripherals, manage MCU low power modes (DOZE, STOP and WAIT) by disabling peripheral clocks and other clock related features. This module also includes the control logic for asserting soft and hard chip-level system resets.

#### 22) External Interrupt Module (INT)

This module provides control for five of the eight external interrupt sources. Each pin is individually configurable as a level-sensitive interrupt, an edge-detecting (rising, falling, or both) interrupt, or a general purpose I/O. Each pin has a dedicated interrupt line.

# 4.2.3 Shared Peripherals

Shared peripherals are peripherals that can be accessed by both the DSP and MCU cores. The functionality of these peripherals is detailed below.

# 4.2.3.1 Universal Serial Bus Module (USB)

The USB module provides the required buffering and protocol to communicate on the Universal Serial Bus. The module is provided with an access port for the DSP and for the MCU. The module will act as a USB device only. Host functionality will not be supported. All four types of USB data transfers are supported: control, isochronous, interrupt, and bulk

# 4.2.3.2 General Purpose I/O (GPIO)

The GPIO module is a stand alone module that serves as the all-in-one communication link between the outside world, the MCU module, and the DSP module. The GPIO module will be implemented as a stand-alone module. The GPIO module will provide the following functionality:

- Standard GPIO functionality

- Multiplexed output functionality

- Alternate input functionality

- Shared Access for DSP and MCU

- MCU, DSP interrupt capability

- Interrupt visibility

# 4.2.3.3 MCU / DSP Interface (MDI)

The MDI is the communication interface between the DSP and MCU cores. Through this module, each core can access shared memory, messaging registers, and flags. This module also allows each core to interrupt the other, monitor the low power state of the other core, and other useful functions.

# 4.2.3.4 Layer 1 Timer (L1T)

The Layer 1 Timer module allows for control of all the radio channel timings. Its main function is to unload the MCU from having to schedule events associated with the radio air interface. The timer provides the user a great deal of flexibility in scheduling and executing events using the programmable event tables and macros.

# 4.3 Neptune GPIO Summary

Neptune GPIO module is a stand alone module that serves as the all-in-one communication link between the outside world, the MCU module and the DSP module. The GPIO communicates with the MCU through the IP Bus and to the DSP through the DSP Peripheral Bus. The GPIO module houses five 16 pin bi-directional Ports.

# 4.4 Neptune-LTE Memory Interface

Although Neptune has internal ROM and RAM, it still needs external memory chipsets for its operation. One 32Mbit Flash and one 4Mbit SRAM can access by Neptune via the 16-bit parallel data bus. Each of these devices is assigned a specific chip enable(s) from the Neptune-LTE.

The detailed information of Flash and SRAM is described as following.

# 4.4.1 Flash

The Flash used in E2 phone design is Intel W18 series Flash product. The 1.8 Volt Intel® Wireless Flash memory provides RWW/RWE capability with high performance synchronous and asynchronous reads on package-compatible densities with a 16-bit data bus.

# 4.4.2 PSRAM

The memory size used in E2 phone design is 16 Mega bits (2 Mega bytes).

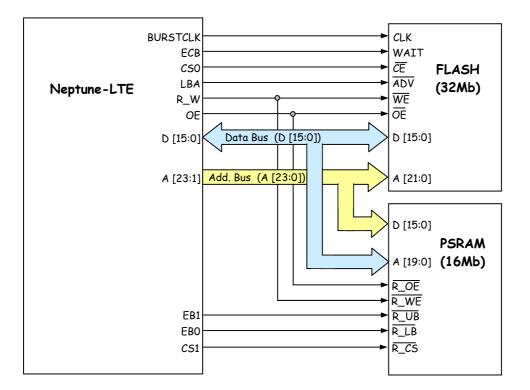

#### 4.4.3 Neptune-LTE Chip Select Assignments

The ARM External Memory Interface Module (handles the interface to devices external to an ARM architecture based chip, including generation of chip selects for external peripherals and memory.

The six Chip Selects assigned as in **Fehler! Verweisquelle konnte nicht gefunden** werden.

| Pin Name | Pin # | Туре | Active H/L | Description          |

|----------|-------|------|------------|----------------------|

| CS0      | P15   | 0    | L          | Flash Chip Selection |

| CS1      | R15   | 0    | L          | SRAM Chip Selection  |

#### Table 3 - Neptune-LTE Chip Select Assignment

EB0 \* and EB1 \* are assignment as the Byte selection for SRAM access. EB0 \* is for SRAM lower byte and EB1 \* is for SRAM upper byte access.

The memory connection with Neptune-LTE shows in **Fehler! Verweisquelle konnte** nicht gefunden werden.

Figure 16 – E2 Baseband Neptune-LTE and Memory Connection Block Diagram

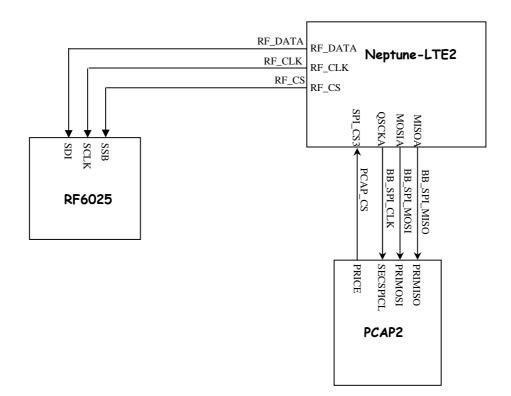

# 4.5 Neptune MQSPI Module

The MQSPI (Multiple Queue Serial Peripheral Interface) performs the serial programming operations to configure radio subsystems and selected peripherals. In this dual SPI configuration, the system is typically partitioned into RF and baseband functions. This peripheral is designed to minimize the amount of MCU interaction necessary for multiple serial data transfers. The MQSPI module in Neptune has the following features:

- Full-Duplex, Three-Wire Synchronous Transfers

- Half-Duplex, Two-Wire Synchronous Transfers

- Programmable Bit Rates

- Programmable Inactive Clock Polarity

- Programmable Chip Select Polarity

- Ten Chip Select Pins

- 256 X 16 bit of RAM for Data I/O Storages sharable by both SPIs

- Programmable Transfer Length from 1 to 32 Bytes

- Programmable Multiple Message from 1 to 64 Messages

- Each SPI functions only as a master SPI

- Dual Independently Functioning SPIs

- 32 Configurable Control Queues/Triggers

- 64 Programmable Control Data Registers (32 Mode and 32 Pointer Registers)

- Four FIFO Queues a High and Low Priority Queue for Each SPI

- 32 One-Cold Trigger Signals From the Layer 1 Timer

- MCU Controlled Trigger Register

- Two Interrupt Lines One for Each SPI

- Programmable Data Change on Rising/Falling Clock Edge

- Programmable Data Latch on Rising/Falling Clock Edge

- Separate Read/Write Data I/O Storage Pointers

- Burst and multiple message transfers

- Programmable 128 Clock Delay Before First Clock Edge

- Programmable 128 Clock Delay After Transfer

- Transmit and receive Data is LSB/MSB Selectable

- DOZE Mode Capability

- Serial Display Interface

E2 quad-band EDGE / GPRS GSM uses a dedicated RF SPI port for RF6025 data writing. And one MQSPI port is used to access with PCAP2 and the chip selection is SPI\_CS3. The connection between Neptune-LTE and PCAP2, RF6025 shows in **Fehler!** Verweisquelle konnte nicht gefunden werden.

Figure 17 - Neptune MQSPI Connection with PCAP2 and RF6025 Block Diagram

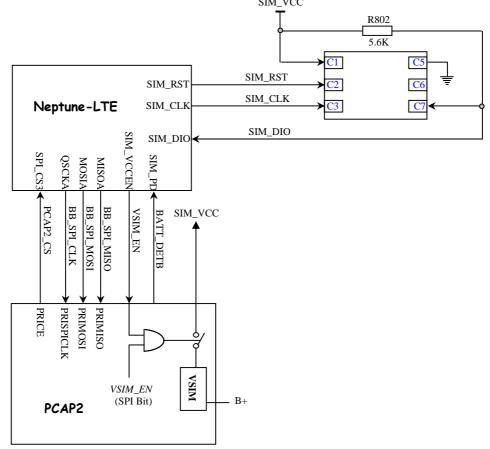

## 4.6 SIM Interface

The SIM Interface Module (SIM) is designed to facilitate communication to SIM cards or Eurochip pre-paid phone cards. The SIM module has two ports that can be used to interface with the various cards. The SIM connection in E2 shows in **Fehler! Verweisquelle konnte nicht gefunden werden.** diagram. <sub>SIM\_VCC</sub>

Figure 18 – E2 SIM Connection Block Diagram

E2 doesn't use PCAP2 internal level shifters for 5V SIM card support due to the fact that Neptune-LTE multiplexed the SIM data input and output together. E2 can only support 3V SIM card and no 1.8V & 5V SIM support.

The SIM detect circuit is actually a battery detection circuit in E2 design. When one of the following conditions occurs, the BATT\_DETB output asserted logic 0 to indicate battery presence.

- A thermistor (with effective resistance < 38K approx) is connected to the AD4 input

- The BATT+ (battery) voltage exceeds REF2 threshold

- MOBPORTB is present AND the BATT\_DET\_IN signal is grounded

The PCAP2 battery detection circuit block diagram shows in **Fehler! Verweisquelle konnte nicht gefunden werden.**

Figure 19 – E2 SIM Present Detection Circuit Logic Block Diagram

A battery must be inserted to pull the BATT\_DETB (Neptune pin name is SIM\_PD) line low. Software shall check to see if this line is low. If it is not low then that indicates that a battery is not present and software shall write "Insert Battery" to the display. When a battery is not present, BATT\_DETB is pulled high with V2 (2.775 V). If a battery is present, then BATT\_DETB is pulled low and software shall then attempt to read from the SIM card. If it does not read any data from the SIM on the SIM\_I/O line then that indicates that a card is not present and software writes "Check Card" to the display.

## E2 Level 3 Circuit Description

| <b>Battery Present</b> | SIM Card Present | <b>Display Message</b> | Comment                                    |

|------------------------|------------------|------------------------|--------------------------------------------|

| No                     | No               | "Insert Battery"       | Phone may be powered via EXT_B+            |

| No                     | Yes              | "Insert Battery"       | Phone may be powered via EXT_B+            |

| Yes                    | No               | "Check Card"           | Phone may be powered via battery or EXT_B+ |

| Yes                    | Yes              |                        | Allow full phone functionality to user     |

#### Table 4 - SIM Card Presence Detect Matrix

Fehler! Verweisquelle konnte nicht gefunden werden. shows the SIM card presence detection matrix.

A battery, whether it is good (above software voltage threshold for shutdown) or bad (below software voltage threshold for power up), must be inserted to the phone to pull BATT\_DETB low. If the user cannot power the phone up with the battery alone, then he or she must insert the AC Adapter as well a battery with internal thermistor to use the phone. In all the above cases, EMERGENCY CALLS are allowed.

## **5** Neptune-LTE RF Interface

E2 RF interface includes two separate ICs.

This section describes the interface between the Neptune LTE2 and the RF section (RFMD PRiME 2 chipset). There are two chipsets for RFMD GPRS / EDGE solutions. A brief descriptions for those chips functions etc are introduced below.

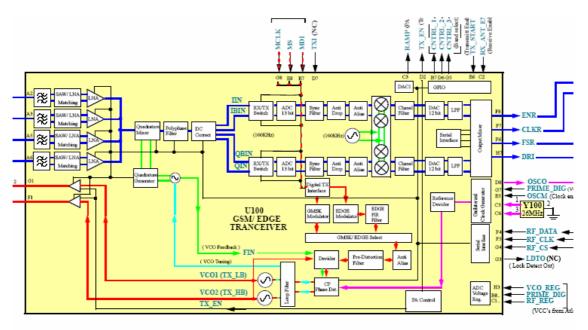

## 5.1.1 RF6025 Functional Description

The Polaris RF6025 transceiver module is a highly integrated transceiver intended for quad-band GSM/GPRS/EDGE applications. Included, in the module, are integrated RX SAW filters, integrated TX power VCOs and a RX VCO, a GMSK modulator; a 8PSK modulator; PA ramp control and reference oscillator circuitry for an off-module crystal oscillator.

Configuration of the transceiver is accomplished by setting internal registers via a 3-wire serial interface that connects directly to the baseband controller (Neptune). In receive, the RF6025 accepts four inputs from the switchplexer (one for each RX band) and after down-conversion and filtering sends RX I/Q data to the baseband. The output format may be either analog or digital. In transmit, the RF6025 module takes either analog I/Q data or the TX symbol data from the baseband, uses this to modulate the TX VCO and control the PA ramping signal to the PA or transmit module. The switchplexer may also be controlled with the general purpose output lines in the module.

The fractional-N synthesizer section is multiplexed between transmit and receive functions, creating two sets of PLL parameters. The PLLx0 register determines the state in which the PLL is working. Each PLL configuration has a fully integrated loop filter. The RF6025 module has a buffered oscillator output that provides either a 13MHz or 26MHz reference output for use by the baseband. The frequency of this buffered output is user selectable.

The internal power VCO's are designed for use in the following frequency ranges: VCO1 has a frequency range of 824MHz to 915MHz; and, VCO2 has a frequency range of 1710MHz to 1910MHz. Each VCO is buffered and has a +4dBm minimum output power.

Downconversion from VLIF to baseband, and all necessary baseband filtering for GSM/GPRS/EDGE reception, is implemented digitally, with programmable bandwidths ranging from 80kHz to 135kHz.

The polar modulator used for EDGE transmit is shown below. In EDGE mode, both digital and analog interfaces are available. The RF6025 performs all of the necessary pulse shaping, and maps the data bits into amplitude and phase components for the required modulation. The phase component is pre-distorted to account for the PLL loop filter roll off and then combined with the channel selection word of the Fractional-N (FN) synthesizer, which is directly modulated onto the internal VCO. The amplitude components are scaled according to the PA ramping control signal and directly applied to the PA collector voltage control system (in the RF3144). The amplitude component in this way is directly modulated onto the PA output. **Fehler! Verweisquelle konnte nicht gefunden werden.** shows the RF6025

Figure 20 - RF6025 Functional Block Diagram

The GSM receive and transmit baseband interfaces can be configured to work with standard analog differential I/Q signals or fully digital signals depending on SDI programming. The GMSK modulator necessary for GSM signaling is also provided and feeds into the transmit FN synthesizer for direct modulation of the VCO's. There are two D/As (DAC1/DAC2) provided: DAC1 is configured to provide programmable ramp control for the PA; and, DAC2 for generalpurpose DC tuning voltage applications. An automatic PA ramp control function is provided, ramp shaping and timing and is the same for both GMSK and 8PSK modulation types.

## 5.1.2 RF6025 Serial Data Interface and Device Control

A three wire serial data interface allows user programming of the internal control registers in the RF6025. The serial data interface consists of the serial select (SSB), serial data in (SDI) and serial clock (SCLK) pins. The lock detect/test out (LDTO) pin is by default configured as an output from the serial interface, but may be used to monitor various internal PLL signals, as well.

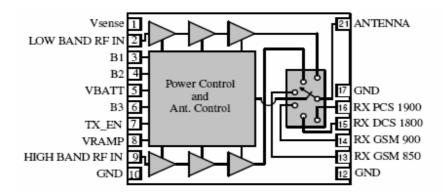

## 5.2 RF3178 (Quad-Band Power Amplifier Module) Chipset

The 3144 module is a 50W input/output, quad-band, dual-mode, GMSK/8PSK(EDGE) PA module intended for 2.75G radio applications. The module consists of a dual line-up power amplifier, harmonic filter, and antenna switch. The antenna connects the antenna to any one of four receiver ports or either low band power amplifier output or high band power amplifier output. The module contains two RF dies using HBT technology, a silicon die for the power control and antenna switch controller, a harmonic filter, an DC blocks at all RF ports. The module incorporates an indirect closed loop method for power control. Output power is controlled by varying the collector voltage. The module does not have any filters/coupler/detector.

This PA module is used in the final amplification stages in a GSM portable telephone operating in either GMSK or EDGE mode. For the EDGE mode, this PA is best suited for systems employing Polar Modulation method where in the amplifier operates compression all the time.

No serial interface needs to provide control to this chipset during its operation

Figure 21 - RF3178 Functional Block Diagram

## E2 Level 3 Circuit Description

| TX module mode            |       | Control Pins |    |    |  |  |  |  |

|---------------------------|-------|--------------|----|----|--|--|--|--|

| I A module mode           | TX_EN | B1           | B2 | B3 |  |  |  |  |

| Low power standby mode    | 0     | 0            | 0  | 0  |  |  |  |  |

| RX850                     | 0     | 0            | 0  | 1  |  |  |  |  |

| RX900                     | 0     | 1            | 0  | х  |  |  |  |  |

| RX1800                    | 0     | 0            | 1  | х  |  |  |  |  |

| RX1900                    | 0     | 1            | 1  | х  |  |  |  |  |

| TX low band, low output   | 1     | х            | 0  | 0  |  |  |  |  |

| power range (VCC3 OFF)    |       |              |    |    |  |  |  |  |

| TX low band, high output  | 1     | х            | 0  | 1  |  |  |  |  |

| power range               |       |              |    |    |  |  |  |  |

| TX high band, low output  | 1     | х            | 1  | 0  |  |  |  |  |

| power range (VCC3 OFF)    |       |              |    |    |  |  |  |  |

| TX high band, high output | 1     | х            | 1  | 1  |  |  |  |  |

| power range               |       |              |    |    |  |  |  |  |

The band , receiver and transmit control true table shows in **Fehler! Verweisquelle konnte nicht gefunden werden.**

| <b>Table 5 - RF3178</b> | Antenna Switch | <b>Control True Table</b> |

|-------------------------|----------------|---------------------------|

|                         |                |                           |

#### 6 Application Processor (Bulverde)

#### 6.1 Bulverde Functional Overview

The Bulverde processor is an integrated system-on-a-chip microprocessor for high performance, dynamic, low-power portable handheld and handset devices. It incorporates the Intel® XScale<sup>TM</sup> microarchitecture with voltage and frequency scaling and sophisticated power management to provide excellent MIPs/mW performance. The processor complies with the ARM\* version 5TE instruction set (excluding floating-point instructions) and follows the ARM\* programmer's model. The Bulverde processor also provides Intel® Wireless MMX<sup>TM</sup> media enhancement technology, which supports integer instructions to accelerate audio and video processor.

Bulverde has the following features:

- Core frequencies supported

- 200 MHz for the PXA261 processor

- 200 300 MHz for the PXA262 processor

- System memory interface

- > 100MHz SDRAM

- ▶ 4 MB to 256 MB of SDRAM memory

- Support for 16, 64, 128, or 256Mbit DRAM technologies

- ➤ 4 Banks of SDRAM, each supporting 64 MB of memory

- Clock enable (CKE) provides 1 CKE pin to put the entire SDRAM interface into self refresh

- Supports as many as 5 external static memory devices (SRAM, flash, or VLIO) and 1 internal flash device

- PCMCIA/Compact Flash card control pins

- LCD Controller pins

- Full-function UART

- Bluetooth UART

- Hardware UART

- MMC Controller pins

- SSP pins

- Network SSP

- Audio SSP

- USB Client pins

- AC'97 Controller pins

- Standard UART pins

- I2C Controller pins

- PWM pins

- 20 dedicated GPIOs pins

- Integrated JTAG support

- Single-Ended USB client

18<sup>th</sup> Aug 2006

#### 6.2 Bulverde Memory Interface

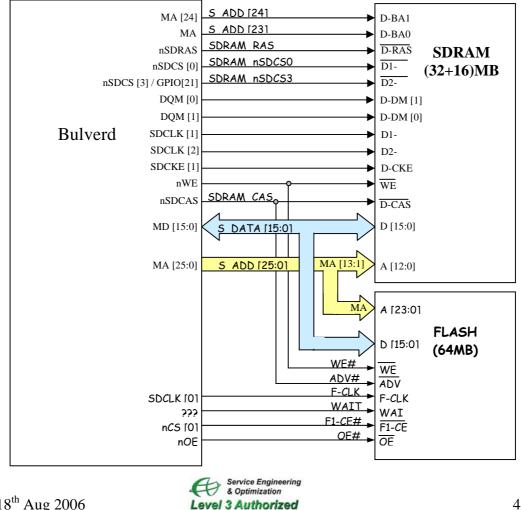

E2 uses Intel 64MB Flash + 48MB SDRAM stack memory as application memory chipset.

The connection of Bulverde and memory shows in Fehler! Verweisquelle konnte nicht gefunden werden.

#### 6.2.1 Bulverde SDRAM Interface

The processor supports an SDRAM interface at a maximum frequency of 100 MHz. The SDRAM interface supports four 16-bit or 32-bit wide SDRAM partitions. Each partition is allocated 64 MBytes of the internal memory map. However, the actual size of each partition is dependent on the particular SDRAM configuration used. The four partitions are divided into two partition pairs: the 0/1 pair and the 2/3 pair. Both partitions within a pair (for example, partition 0 and partition 1) must be identical in size and configuration; however, the two pairs can be different. For example, the 0/1 pair can be 100 MHz SDRAM on a 32-bit data bus, while the 2/3 pair can be 50 MHz SDRAM on a 16-bit data bus.

E2 assigns 32MB SDRAM in pair 0 and 16MB SDRAM in pair 1.

E2 Level 3 Circuit Description

# Figure 22 - Bulverde Memory Connection Block Diagram

In this diagram, each SDRAM signal functions as below:

- **S\_DATA** [15:0] Data Input / Output pins.

- S\_ADD [12:0] During a Bank Activate command cycle, those signals define the row address (RA0 RA12) when sampled at the rising clock edge. During a Read or Write command cycle, S\_ADD [0] S\_ADD [n] define the column address (CA0 CAn) when sampled at the rising clock edge. CAn depends from the SDRAM organization. In addition to the column address, S\_ADD [10] (=AP) is used to invoke autoprecharge operation at the end of the burst read or write cycle. If S\_ADD [10] is high, autoprecharge is selected and BA0, BA1 defines the bank to be precharged. If S\_ADD [10] is low, autoprecharge is disabled. During a Precharge command cycle, S\_ADD [10] (=AP) is used in conjunction with BA0 and BA1 to control which bank(s) to precharge. If A10 is high, all four banks will be precharged regardless of the state of BA0 and BA1. If A10 is low, then BA0 and BA1 are used to define which bank to precharge.

- S\_ADD [23] & S\_ADD [24] Bank Select Inputs. Selects which bank is to be active.

- SDRAM\_RAS & SDRAM\_CAS When sampled at the positive rising edge of the clock, those two signals and SDRAM\_nWE define the command to be executed by the SDRAM. SDRAM\_LDQM & SDRAM\_UDQM The Data Input / Output mask places the DQ buffers in a high impedance state when sampled high. In Read mode, DQM has a latency of two clock cycles and controls the output buffers like an output enable. In Write mode, DQMx has a latency of zero and operates as a word mask by allowing input data to be written if it is low but blocks the write operation if DQM is high. LDQM and UDQM control the lower and upper bytes in x16 SDRAM.

- **SDRAM\_CLK1** The system clock input. This clock input is for 32MB SDRAM die. All of the SDRAM inputs are samples on the rising edge of the clock.

- **SDRAM\_CLK2** The system clock input. This clock input is for 16MB SDRAM die. All of the SDRAM inputs are samples on the rising edge of the clock.

- **SDRAM\_CKE1** Activates the clock signal when high and deactivates the CLK signal when low, thereby initiates either the Power Down mode, Suspend mode, or the Self Refresh mode.

- **SDRAM\_nSDCS0** This signal enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue. This input is for 32MB SDRAM die chip-select.